# Code Generation for Data Processing

Lecture 1: Introduction and Interpretation

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2024/25

# Module "Code Generation for Data Processing"

#### Learning Goals

- ▶ Getting from an intermediate code representation to machine code

- Designing and implementing IRs and machine code generators

- ▶ Apply for: JIT compilation, query compilation, ISA emulation

# Module "Code Generation for Data Processing"

#### Learning Goals

- ▶ Getting from an intermediate code representation to machine code

- Designing and implementing IRs and machine code generators

- Apply for: JIT compilation, query compilation, ISA emulation

#### Prerequisites

Computer Architecture, Assembly

ERA, GRA/ASP

► Databases, Relational Algebra

GDB

▶ Beneficial: Compiler Construction, Modern DBs

3

#### Introduction

- ► Introduction and Interpretation

- ► Compiler Front-end

#### Introduction

- ► Introduction and Interpretation

- ► Compiler Front-end

#### Intermediate Representations

- ► IR Concepts and Design

- ► LLVM-IR

- Analyses and Optimizations

#### Introduction

- ► Introduction and Interpretation

- Compiler Front-end

#### Intermediate Representations

- ► IR Concepts and Design

- ► LLVM-IR

- Analyses and Optimizations

#### Compiler Back-end

- Instruction Selection

- Register Allocation

- ► Linker, Loader, Debuginfo

3

#### Introduction

- ► Introduction and Interpretation

- ► Compiler Front-end

#### Intermediate Representations

- ► IR Concepts and Design

- ► LLVM-IR

- Analyses and Optimizations

#### Compiler Back-end

- ► Instruction Selection

- Register Allocation

- Linker, Loader, Debuginfo

#### **Applications**

- JIT-compilation + Sandboxing

- Query Compilation

- ► Binary Translation

3

#### Lecture Organization

- ► Lecturer: Dr. Alexis Engelke engelke@in.tum.de

- ► Time slot: Thu 10-14, 02.11.018

- ▶ Material: https://db.in.tum.de/teaching/ws2425/codegen/

#### Exam

- Written exam, 90 minutes, no retake, date TBD

- ► (Might change to oral on very low registration count)

#### **Exercises**

- ▶ Regular homework, often with programming exercise

- Submission via POST request (see assignments)

- Grading with  $\{*,+,\sim,-\}$ , feedback on best effort

- Exercise session modes:

- Present and discuss homework solutions

- Hands-on programming or analysis of systems (needs laptop)

#### Grade Bonus

- Requirement: N-2 "sufficiently working" homework submissions and one presentations of homework in class (depends on submission count)

- ▶ Bonus: grades in [1.3; 4.0] improved by 0.3/0.4

5

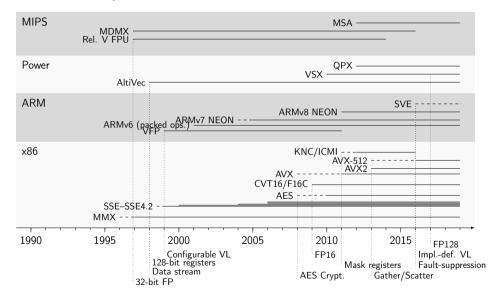

# Why study compilers?

- Critical component of every system, functionality and performance

- ► Compiler mostly *alone* responsible for using hardware well

- Brings together many aspects of CS:

- ► Theory, algorithms, systems, architecture, software engineering, (ML)

- New developments/requirements pose new challenges

- ▶ New architectures, environments, language concepts, . . .

- High complexity!

# Compiler Lectures @ TUM

Compiler Construction IN2227, SS. THEO

Front-end, parsing, semantic analyses, types

Program Optimization IN2053. WS. THEO

Analyses, transformations, abstract interpretation

Virtual Machines IN2040, SS. THEO

Mapping programming paradigms to IR/bytecode

Programming Languages CIT3230000, WS

Implementation of advanced language features

Code Generation CIT3230001, WS

Back-end, machine code generation, JIT comp.

Why study code generation?

#### Why study code generation?

- ► Frameworks (LLVM, ...) exist and are comparably good, but often not good enough (performance, features)

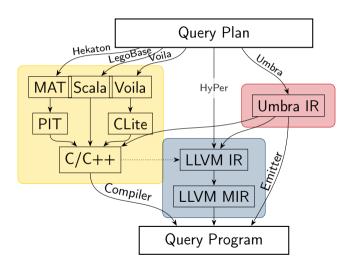

- Many systems with code gen. have their own back-end

- ► E.g.: V8, WebKit FTL, .NET RyuJIT, GHC, Zig, QEMU, Umbra, . . .

# Why study code generation?

- ► Frameworks (LLVM, ...) exist and are comparably good, but often not good enough (performance, features)

- Many systems with code gen. have their own back-end

- ► E.g.: V8, WebKit FTL, .NET RyuJIT, GHC, Zig, QEMU, Umbra, . . .

- ► Machine code is not the only target: bytecode

- Often used for code execution

- ► E.g.: V8, Java, .NET MSIL, BEAM (Erlang), Python, MonetDB, eBPF, ...

- Allows for flexible design

- ▶ But: efficient execution needs machine code generation

# Proebsting's Law

# Proebsting's Law

"Compiler advances double computing power every 18 years."

- Todd Proebsting, 1998<sup>1</sup>

# Proebsting's Law

"Compiler advances double computing power every 18 years."

- Todd Proebsting, 1998<sup>1</sup>

▶ Still optimistic; depends on number of abstractions

## Motivational Example: Brainfuck

- Turing-complete esoteric programming language, 8 operations

- ► Input/output: . ,

- Moving pointer over infinite array: < >

- ► Increment/decrement: + -

- ▶ Jump to matching bracket if (not) zero: []

► Execution with pen/paper? ∴

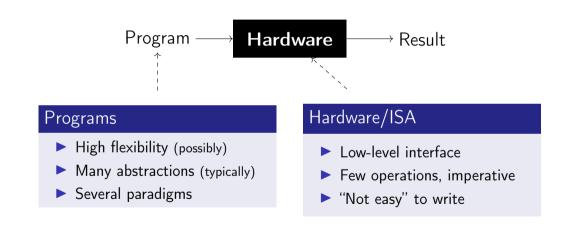

$\mathsf{Program} \longrightarrow \hspace{0.1cm} \textbf{Hardware} \hspace{0.1cm} \longrightarrow \hspace{0.1cm} \mathsf{Result}$

#### Programs

- ► High flexibility (possibly)

- Many abstractions (typically)

- Several paradigms

# Motivational Example: Brainfuck – Interpretation

Write an interpreter!

```

unsigned char state[10000];

unsigned ptr = 0, pc = 0;

while (prog[pc])

switch (prog[pc++]) {

case '.': putchar(state[ptr]); break;

case ',': state[ptr] = getchar(); break;

case '>': ptr++; break;

case '<': ptr--; break;

case '+': state[ptr]++; break;

case '-': state[ptr]--; break;

case '[': state[ptr] || (pc = matchParen(pc, prog)); break;

case ']': state[ptr] && (pc = matchParen(pc, prog)); break;

}

```

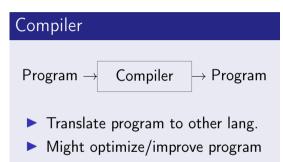

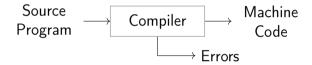

#### Compiler

$\mathsf{Program} \to \mathsf{Compiler} \quad \to \mathsf{Program}$

- ► Translate program to other lang.

- ► Might optimize/improve program

#### Compiler

$\mathsf{Program} \to \mathsf{Compiler} \quad \to \mathsf{Program}$

- ► Translate program to other lang.

- Might optimize/improve program

- ightharpoonup C, C++, Rust ightharpoonup machine code

- ightharpoonup Python, Java ightharpoonup bytecode

# Compiler Program → Compiler → Program Translate program to other lang.

ightharpoonup C, C++, Rust ightarrow machine code

► Might optimize/improve program

ightharpoonup Python, Java ightharpoonup bytecode

#### Interpreter

$\mathsf{Program} \to \mathsf{Interpreter} \longrightarrow \mathsf{Result}$

- Directly execute program

- Computes program result

#### Compiler

$\mathsf{Program} \to \mathsf{Compiler} \quad \to \mathsf{Program}$

- Translate program to other lang.

- Might optimize/improve program

- ightharpoonup C, C++, Rust ightharpoonup machine code

- ightharpoonup Python, Java ightharpoonup bytecode

#### Interpreter

$\mathsf{Program} \to \mathsf{Interpreter} \longrightarrow \mathsf{Result}$

- Directly execute program

- Computes program result

- Shell scripts, Python bytecode, machine code (conceptually)

- ightharpoonup C, C++, Rust ightharpoonup machine code

- ightharpoonup Python, Java ightharpoonup bytecode

#### Interpreter

$\mathsf{Program} \to \mathsf{Interpreter} \longrightarrow \mathsf{Result}$

- Directly execute program

- Computes program result

- Shell scripts, Python bytecode, machine code (conceptually)

Multiple compilation steps can precede the "final interpretation"

► Targets: machine code, bytecode, or other source language

- ► Targets: machine code, bytecode, or other source language

- Typical goals: better language usability and performance

- ▶ Make lang. usable at all, faster, use less resources, etc.

- ► Targets: machine code, bytecode, or other source language

- Typical goals: better language usability and performance

- ▶ Make lang. usable at all, faster, use less resources, etc.

- Constraints: specs, resources (comp.-time, etc.), requirements (perf., etc.)

- Examples:

- Targets: machine code, bytecode, or other source language

- ► Typical goals: better language usability and performance

- ► Make lang. usable at all, faster, use less resources, etc.

- Constraints: specs, resources (comp.-time, etc.), requirements (perf., etc.)

- Examples:

- ► "Classic" compilers source → machine code

- ▶ JIT compilation of JavaScript, WebAssembly, Java bytecode, . . .

- Database query compilation

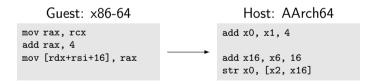

- ► ISA emulation/binary translation

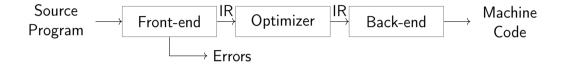

# Compiler Structure: Monolithic

#### Compiler Structure: Monolithic

► Inflexible architecture, hard to retarget

## Compiler Structure: Two-phase architecture

# Compiler Structure: Two-phase architecture

#### Front-end

- Parses source code

- ► Detect syntax/semantical errors

- ► Emit *intermediate representation* encode semantics/knowledge

- ▶ Typically:  $\mathcal{O}(n)$  or  $\mathcal{O}(n \log n)$

# Compiler Structure: Two-phase architecture

#### Front-end

- Parses source code

- Detect syntax/semantical errors

- ► Emit *intermediate representation* encode semantics/knowledge

- ► Typically:  $\mathcal{O}(n)$  or  $\mathcal{O}(n \log n)$

#### Back-end

- ► Translate IR to target architecture

- ► Can assume valid IR (~ no errors)

- Possibly one back-end per arch.

- ightharpoonup Contains  $\mathcal{NP}$ -complete problems

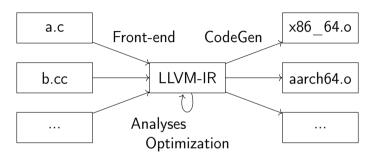

# Compiler Structure: Three-phase architecture

# Compiler Structure: Three-phase architecture

Optimizer: analyze/transform/rewrite program inside IR

# Compiler Structure: Three-phase architecture

- Optimizer: analyze/transform/rewrite program inside IR

- Conceptual architecture: real compilers typically much more complex

- Several IRs in front-end and back-end, optimizations on different IRs

- ► Multiple front-ends for different languages

- Multiple back-ends for different architectures

- 1. Tokenizer: recognize words, numbers, operators, etc.

- ightharpoonup Example: a+b\*c ightharpoonup ID(a) PLUS ID(b) TIMES ID(c)

$\mathcal{R}e$

1. Tokenizer: recognize words, numbers, operators, etc.

$\mathcal{R}e$

- ightharpoonup Example: a+b\*c ightharpoonup ID(a) PLUS ID(b) TIMES ID(c)

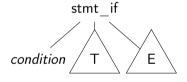

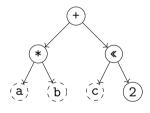

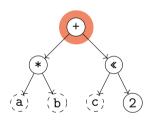

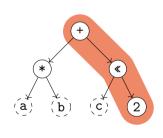

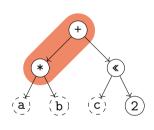

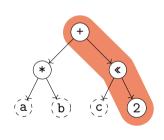

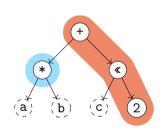

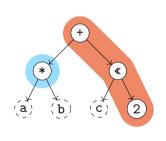

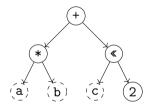

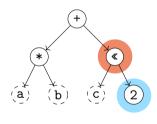

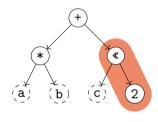

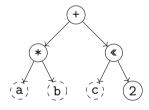

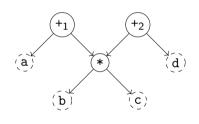

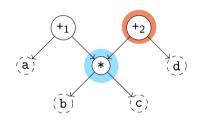

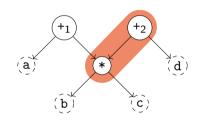

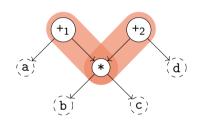

- 2. Parser: build (abstract) syntax tree, check for syntax errors

$\mathcal{CFG}$

- ➤ Syntax Tree: describe grammatical structure of complete program

Example: expr("a", op("+"), expr("b", op("\*"), expr("c"))

- Abstract Syntax Tree: only relevant information, more concise Example: plus("a", times("b", "c"))

1. Tokenizer: recognize words, numbers, operators, etc.

$\mathcal{R}e$

- ightharpoonup Example: a+b\*c ightharpoonup ID(a) PLUS ID(b) TIMES ID(c)

- 2. Parser: build (abstract) syntax tree, check for syntax errors

$\mathcal{CFG}$

- ➤ Syntax Tree: describe grammatical structure of complete program Example: expr("a", op("+"), expr("b", op("\*"), expr("c"))

- ► Abstract Syntax Tree: only relevant information, more concise Example: plus("a", times("b", "c"))

- 3. Semantic Analysis: check types, variable existence, etc.

1. Tokenizer: recognize words, numbers, operators, etc.

$\mathcal{R}e$

- ightharpoonup Example: a+b\*c  $\rightarrow$  ID(a) PLUS ID(b) TIMES ID(c)

- 2. Parser: build (abstract) syntax tree, check for syntax errors

$\mathcal{CFG}$

- ➤ Syntax Tree: describe grammatical structure of complete program Example: expr("a", op("+"), expr("b", op("\*"), expr("c"))

- ► Abstract Syntax Tree: only relevant information, more concise Example: plus("a", times("b", "c"))

- 3. Semantic Analysis: check types, variable existence, etc.

- 4. IR Generator: produce IR for next stage

- ► This might be the AST itself

- 1. Instruction Selection: map IR operations to target instructions

- ▶ Use target features: special insts., addressing modes, . . .

- ► Still using virtual/unlimited registers

- 1. Instruction Selection: map IR operations to target instructions

- Use target features: special insts., addressing modes, . . .

- ► Still using virtual/unlimited registers

- 2. Instruction Scheduling: optimize order for target arch.

- Start memory/high-latency earlier, etc.

- ► Requires knowledge about micro-architecture

- 1. Instruction Selection: map IR operations to target instructions

- ▶ Use target features: special insts., addressing modes, . . .

- Still using virtual/unlimited registers

- 2. Instruction Scheduling: optimize order for target arch.

- Start memory/high-latency earlier, etc.

- Requires knowledge about micro-architecture

- 3. Register Allocation: map values to fixed register set/stack

- ▶ Use available registers effectively, minimize stack usage

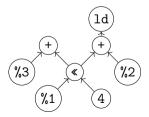

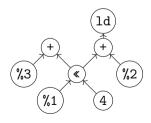

# Motivational Example: Brainfuck - Front-end

- ► Need to skip comments

- ► Bracket searching is expensive/redundant

- ► Idea: "parse" program!

- ► Tokenizer: yield next operation, skipping comments

- ▶ Parser: find matching brackets, construct AST

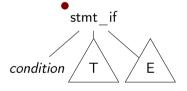

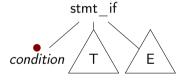

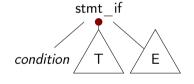

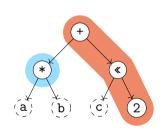

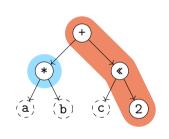

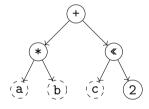

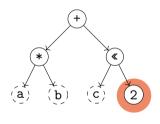

### Motivational Example: Brainfuck – AST Interpretation

► AST can be interpreted recursively

```

struct node { char kind; unsigned cldCnt; struct node* cld; };

struct state { unsigned char* arr; size_t ptr; };

void donode(struct node* n, struct state* s) {

switch (n->kind) {

case '+': s->arr[s->ptr]++; break;

// ...

case '[': while (s->arr[s->ptr]) children(n, s); break;

case 0: children(n, s); break; // root

void children(struct node* n, struct state* s) {

for (unsigned i = 0; i < n->cldCnt; i++) donode(n->cld + i, s);

```

- ▶ Inefficient sequences of +/-/</> can be combined

- ► Trivially done when generating IR

- ▶ Inefficient sequences of +/-/</> can be combined

- ► Trivially done when generating IR

- ► Fold patterns into more high-level operations

Look at some Brainfuck programs. Which patterns are beneficial to fold?

- ► Fold offset into operation

- ▶ right(2) add(1) = addoff(2, 1) right(2)

- ► Also possible with loops

- Fold offset into operation

- right(2) add(1) = addoff(2, 1) right(2)

- Also possible with loops

- Analysis: does loop move pointer?

- Loops that keep position intact allow more optimizations

- Maybe distinguish "regular loops" from arbitrary loops?

- ► Get rid of all "effect-less" pointer movements

- Fold offset into operation

- ▶ right(2) add(1) = addoff(2, 1) right(2)

- Also possible with loops

- Analysis: does loop move pointer?

- Loops that keep position intact allow more optimizations

- Maybe distinguish "regular loops" from arbitrary loops?

- ► Get rid of all "effect-less" pointer movements

- Combine arithmetic operations, disambiguate addresses, etc.

# Motivational Example: Brainfuck – Bytecode

### Motivational Example: Brainfuck – Bytecode

- ► Tree is nice, but rather inefficient  $\rightsquigarrow$  flat and compact bytecode

- ► Avoid pointer dereferences/indirections; keep code size small

### Motivational Example: Brainfuck – Bytecode

- ► Tree is nice, but rather inefficient → flat and compact bytecode

- Avoid pointer dereferences/indirections; keep code size small

- Maybe dispatch two instructions at once?

- ▶ switch (ops[pc] | ops[pc+1] << 8)

- ▶ Superinstructions: combine common sequences to one instruction

Motivational Example: Brainfuck – Threaded Interpretation

### Motivational Example: Brainfuck - Threaded Interpretation

- ► Simple switch—case dispatch has lots of branch misses

- ▶ Threaded interpretation: at end of a handler, jump to next op

```

struct op { char op; char data; };

struct state { unsigned char* arr; size_t ptr; };

void threadedInterp(struct op* ops, struct state* s) {

static const void* table[] = { &&CASE ADD, &&CASE RIGHT, };

#define DISPATCH do { goto *table[(++pc)->op]; } while (0)

struct op* pc = ops;

DISPATCH:

CASE_ADD: s->arr[s->ptr] += pc->data; DISPATCH;

CASE_RIGHT: s->arr += pc->data; DISPATCH;

```

► Key technique to "avoid" compilation to machine code

- Key technique to "avoid" compilation to machine code

- Preprocess program into efficiently executable bytecode

- Easily identifiable opcode, homogeneous structure

- Can be linear (fast to execute), but trees also work

- lacktriangle Match bytecode ops with needed operations  $\leadsto$  fewer instructions

- Key technique to "avoid" compilation to machine code

- Preprocess program into efficiently executable bytecode

- Easily identifiable opcode, homogeneous structure

- Can be linear (fast to execute), but trees also work

- ▶ Match bytecode ops with needed operations → fewer instructions

- Perhaps optimize if it's worth the benefit

- ► Fold constants, combine instructions, ...

- Consider superinstructions for common sequences

- Key technique to "avoid" compilation to machine code

- Preprocess program into efficiently executable bytecode

- Easily identifiable opcode, homogeneous structure

- Can be linear (fast to execute), but trees also work

- ▶ Match bytecode ops with needed operations → fewer instructions

- Perhaps optimize if it's worth the benefit

- ► Fold constants, combine instructions, ...

- Consider superinstructions for common sequences

- ► For very cold code: avoid transformations at all

## Compiler: Surrounding – Compile-time

► Typical environment for a C/C++ compiler:

- ► Calling Convention: interface with other objects/libraries

- Build systems, dependencies, debuggers, etc.

- Compilation target machine (hardware, VM, etc.)

### Compiler: Surrounding – Run-time

- ► OS interface (I/O, ...)

- ► Memory management (allocation, GC, . . . )

- Parallelization, threads, . . .

- ▶ VM for execution of virtual assembly (JVM, ...)

- Run-time type checking

- Error handling: exception unwinding, assertions, . . .

- Reflection, RTTI

# Motivational Example: Brainfuck - Runtime Environment

# Motivational Example: Brainfuck - Runtime Environment

► Needs I/O for . and ,

## Motivational Example: Brainfuck – Runtime Environment

- ► Needs I/O for . and ,

- ► Error handling: unmatched brackets

## Motivational Example: Brainfuck – Runtime Environment

- ► Needs I/O for . and ,

- ► Error handling: unmatched brackets

- ► Memory management: infinitely sized array

How to efficiently emulate an infinitely sized array?

# Compilation point: AoT vs. JIT

# Compilation point: AoT vs. JIT

#### Ahead-of-Time (AoT)

- All code has to be compiled

- No dynamic optimizations

- Compilation-time secondary concern

#### Just-in-Time (JIT)

- Compilation-time is critical

- Code can be compiled on-demand

- Incremental optimization, too

- Handle cold code fast

- Dynamic specializations possible

- ► Allows for eval()

# Compilation point: AoT vs. JIT

#### Ahead-of-Time (AoT)

- All code has to be compiled

- No dynamic optimizations

- Compilation-time secondary concern

#### Just-in-Time (JIT)

- Compilation-time is critical

- Code can be compiled on-demand

- Incremental optimization, too

- ► Handle cold code fast

- Dynamic specializations possible

- ► Allows for eval()

Various hybrid combinations possible

#### Introduction and Interpretation – Summary

- ► Compilation vs. interpretation and combinations

- Compilers are key to usable/performant languages

- ► Target language typically machine code or bytecode

- Three-phase architecture widely used

- Interpretation techniques: bytecode, threaded interpretation, . . .

- JIT compilation imposes different constraints

## Introduction and Interpretation – Questions

- What is typically compiled and what is interpreted? Why?

- PostScript, C, JavaScript, HTML, SQL

- What are typical types of output languages of compilers?

- How does a compiler IR differ from the source input?

- What is the impact of the language paradigm on optimizations?

- What are important factors for an efficient interpreter?

- ▶ What are key differences between AoT and JIT compilation?

# Code Generation for Data Processing Lecture 2: Compiler Front-end

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2024/25

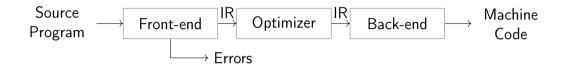

#### Compiler Front-end

- ▶ Typical architecture: separate lexer, parser, and context analysis

- ► Allows for more efficient lexical analysis

- Smaller components, easier to understand, etc.

- ► Some languages: preprocessor and macro expansion

#### Lexer

- ► Convert stream of chars to stream of words (*tokens*)

- ▶ Detect/classify identifiers, numbers, operators, . . .

- ► Strip whitespace, comments, etc.

#### Lexer

- Convert stream of chars to stream of words (tokens)

- Detect/classify identifiers, numbers, operators, . . .

- ► Strip whitespace, comments, etc.

$$a+b*c \rightarrow ID(a)$$

PLUS ID(b) TIMES ID(c)

Typically representable as regular expressions

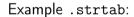

# Typical Token Kinds

# Typical Token Kinds

Punctuators

()[]{};=++=|||

Identifiers

abc123 main

Keywords

$exttt{void int } exttt{\__asm}_-$

Numeric constants

123 Oxab1 5.7e3 Ox1.8p1 09.1f

Char constants

'a' u'œ'

String literals

"abc $\x12\n$ "

Internal

EOF COMMENT UNKNOWN INDENT DEDENT

► Comments might be useful for annotations, e.g. // fallthrough

#### Lexer Implementation

```

struct Token { enum Kind { IDENT, EOF, PLUS, PLUSEQ, /*...*/ }:

std::string_view v; Kind kind; };

Token next(std::string_view v) {

if (v.empty()) return Token{v, Token::EOF};

if (v.starts_with("+=")) return Token{"+="sv, Token::PLUSEQ};

if (v.starts with("+")) return Token{"+"sv, Token::PLUS};

switch (v[0]) {

case ',', '\n', '\t': return next(v.substr(1)); // skip whitespace

case 'a' ... 'z', 'A' ... 'Z'. ' ': {

Token t = // \dots parse identifier, e.g. using regex

if (auto kind = isKeyword(t.v)) return Token{*kind, t.v};

return t:

case '0' ... '9': // ... parse number

default: return Token{v.substr(0, 1), Token::ERROR};

```

# Lexing C??=

```

main() <%

// yay, this is C99??/

puts("hi_world!");

puts("what's_up??!");

%>

```

Output:

# Lexing C??=

```

main() <%

// yay, this is C99??/

puts("hi_world!");

puts("what's_up??!");

%>

Output: what's up|

```

# Lexing C??=

```

main() <%

// yay, this is C99??/

puts("hi_world!");

puts("what's_up??!");

%>

```

Output: what's up |

- ► Trigraphs for systems with more limited encodings/char sets

- Digraphs to provide a more readable alternative...

#### Lexer Implementation

- Essentially a DFA (for most languages)

- ightharpoonup Set of regexes ightharpoonup NFA ightharpoonup DFA

- Respect whitespace/separators for operators, e.g. + and +=

- ► Automatic tools (e.g., flex) exist; most compilers do their own

- Keywords typically parsed as identifiers first

- ► Check identifier if it is a keyword; can use perfect hashing

- Other practical problems

- ▶ UTF-8 homoglyphs; trigraphs; pre-processing directives

#### Parsing

- Convert stream of tokens into (abstract) syntax tree

- ► Most programming languages are context-sensitive

- Variable declarations, argument count, type match, etc.

→ separated into semantic analysis

- Syntactically valid: void foo = doesntExist / "abc";

- Grammar usually specified as CFG

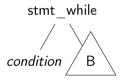

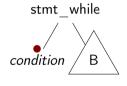

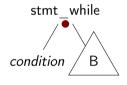

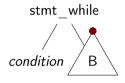

# Context-Free Grammar (CFG)

- ► Terminals: basic symbols/tokens

- ► Non-terminals: syntactic variables

- Start symbol: non-terminal defining language

- ightharpoonup Productions: non-terminal ightarrow series of (non-)terminals

```

\begin{array}{lll} stmt & \rightarrow & whileStmt \mid breakStmt \mid exprStmt \\ whileStmt & \rightarrow & while ( \ expr \ ) \ stmt \\ breakStmt & \rightarrow & break \ ; \\ exprStmt & \rightarrow & expr \ ; \\ expr & \rightarrow & expr + expr \mid expr \ | \ expr = expr \mid ( \ expr \ ) \mid number \end{array}

```

## Hand-written Parsing – First Try

- ► One function per non-terminal

- Check expected structure

- Return AST node

```

NodePtr parseBreakStmt() {

consume(Token::BREAK);

consume(Token::SEMICOLON);

return newNode(Node::BreakStmt);

NodePtr parseWhileStmt() {

consume (Token::WHILE):

consume(Token::LPAREN):

NodePtr expr = parseExpr();

consume (Token::RPAREN):

NodePtr body = parseStmt();

return newNode(Node::WhileStmt,

{expr, body});

NodePtr parseStmt() {

// whoops!

```

#### Hand-written Parsing – First Try

- ► One function per non-terminal

- Check expected structure

- Return AST node

- Need look-ahead!

```

NodePtr parseBreakStmt() {

consume(Token::BREAK);

consume(Token::SEMICOLON);

return newNode(Node::BreakStmt);

NodePtr parseWhileStmt() {

consume (Token::WHILE):

consume(Token::LPAREN):

NodePtr expr = parseExpr();

consume (Token::RPAREN):

NodePtr body = parseStmt();

return newNode(Node::WhileStmt,

{expr, body});

NodePtr parseStmt() {

// whoops!

```

## Hand-written Parsing – Second Try

- ► Need look-ahead to distinguish production rules

- Consequences for grammar:

- No left-recursion

- First n terminals must allow distinguishing rules

- $\triangleright$  LL(n) grammar; n typically 1

- ⇒ Not all CFGs (easily) parseable (but most programming langs. are)

```

NodePtr parseBreakStmt() { /*...*/ }

NodePtr parseWhileStmt() { /*...*/ }

NodePtr parseStmt() {

Token t = peekToken();

if (t.kind == Token::BREAK)

return parseBreakStmt();

if (t.kind == Token::WHILE)

return parseWhileStmt();

NodePtr expr = parseExpr();

consume(Token::SEMICOLON);

return newNode(Node::ExprStmt,

{expr});

```

## Hand-written Parsing – Second Try

- ► Need look-ahead to distinguish production rules

- Consequences for grammar:

- No left-recursion

- First n terminals must allow distinguishing rules

- ightharpoonup LL(n) grammar; n typically 1

- ⇒ Not all CFGs (easily) parseable (but most programming langs. are)

- Now... expressions

```

NodePtr parseBreakStmt() { /*...*/ }

NodePtr parseWhileStmt() { /*...*/ }

NodePtr parseStmt() {

Token t = peekToken();

if (t.kind == Token::BREAK)

return parseBreakStmt();

if (t.kind == Token::WHILE)

return parseWhileStmt();

NodePtr expr = parseExpr():

consume(Token::SEMICOLON);

return newNode(Node::ExprStmt,

{expr});

```

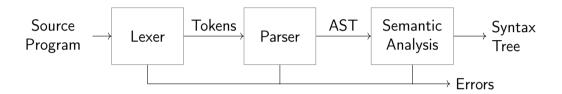

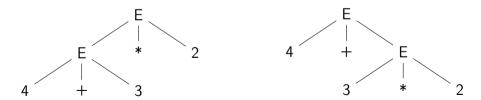

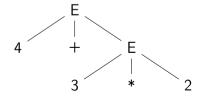

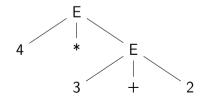

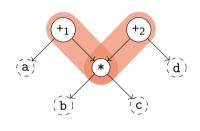

## **Ambiguity**

$$expr \rightarrow expr + expr \mid expr * expr \mid expr = expr \mid ( expr ) \mid number$$

Input:  $4 + 3 * 2$

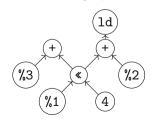

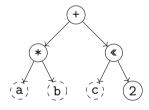

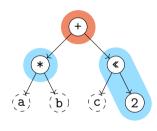

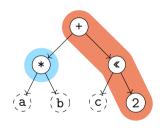

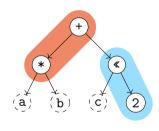

# **Ambiguity**

$$expr \rightarrow expr + expr \mid expr * expr \mid expr = expr \mid (expr) \mid number$$

Input:  $4 + 3 * 2$

## Ambiguity – Rewrite Grammar?

```

primary \rightarrow ( expr ) | number

expr \rightarrow primary + expr | primary * expr | primary = expr | primary

```

## Ambiguity – Rewrite Grammar?

primary

$$\rightarrow$$

( expr ) | number

expr  $\rightarrow$  primary + expr | primary \* expr | primary = expr | primary

Input:  $4 + 3 * 2$  Input:  $4 * 3 + 2$

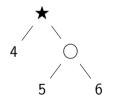

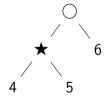

# Ambiguity – Precedence

Input: 4 ★ 5 ○ 6

If  $prec(\bigcirc) > prec(\bigstar)$  or equal prec. and  $\bigstar$  is right-assoc.

If  $prec(\bigcirc) < prec(\bigstar)$  or equal prec. and  $\bigstar$  is left-assoc.

## Hand-written Parsing – Expression Parsing

- ► Start with basic expr.:

- Number, variable, etc.

- Parenthesized expr.

- Parse full expression

- Next token must be )

- Unary expr: followed by expr. with higher prec.

- < unary < []/->

```

NodePtr parseExpr(unsigned minPrec=0);

NodePtr parsePrimaryExpr() {

switch (Token t = next(); t.kind) {

case Token::IDENT:

return makeNode(Node::IDENT, t.v);

case Token::NUMBER: // ...

case Token::MINUS:

// Only exprs with high precedence

return makeNode(Node::UMINUS,

{parseExpr(UNARY_PREC)});

case Token::LPAREN: // ...

// ...

```

## Hand-written Parsing – Expression Parsing

- Only allow ops. with higher prec. on the right child

- ► Right-assoc.: allow same

- ► Lower prec.: return + insert higher up in the tree

```

OpDesc OPS[] = { // {prec, rassoc}}

[Token::MUL] = {12, false},

[Token::ADD] = {11, false},

[Token::EQ] = {2, true},

[Token::QUEST] = {3, true}, // ?:

}

```

```

NodePtr parseExpr(unsigned minPrec=1) {

auto lhs = parsePrimaryExpr();

while (auto op = OPS[next().kind];

op.prec >= minPrec) {

// ... handle (, [, ?: ...

auto newPrec = op.rassoc ?

op.prec : op.prec + 1;

auto rhs = parseExpr(newPrec);

lhs = makeNode(op.nodeKind,

{lhs, rhs});

return lhs;

```

```

a = 3 * 2 + 1;

```

## Hand-written Parsing – Expression Parsing

- Only allow ops. with higher prec. on the right child

- ► Right-assoc.: allow same

- ► Lower prec.: return + insert higher up in the tree

```

OpDesc OPS[] = { // {prec, rassoc}}

[Token::MUL] = {12, false},

[Token::ADD] = {11, false},

[Token::EQ] = {2, true},

[Token::QUEST] = {3, true}, // ?:

}

```

```

NodePtr parseExpr(unsigned minPrec=1) {

auto lhs = parsePrimaryExpr();

while (auto op = OPS[next().kind];

op.prec >= minPrec) {

// ... handle (, [, ?: ...

auto newPrec = op.rassoc ?

op.prec : op.prec + 1;

auto rhs = parseExpr(newPrec);

lhs = makeNode(op.nodeKind,

{lhs, rhs});

return lhs;

```

```

a = 3 * 2 + 1; a = b + c + d = 1; a ? 1 : b ? 2 : 3;

```

## Top-down vs. Bottom-up Parsing

#### Top-down Parsing

- Start with top rule

- Every step: choose expansion

- ► LL(1) parser

- Left-to-right, Leftmost Derivation

- "Easily" writable by hand

- ► Error handling rather simple

- Covers many prog. languages

#### Bottom-up Parsing

- ► Start with text

- Reduce to non-terminal

- ► LR(1) parser

- Left-to-right, Rightmost Derivation

- Strict super-set of LL(1)

- ► Often: uses parser generator

- Error handling more complex

- Covers nearly all prog. languages

#### Parser Generators

- Writing parsers by hand can be large effort

- Parser generators can simplify parser writing a lot

- ➤ Yacc/Bison, PLY, ANTLR, ...

- Automatic generation of parser/parsing tables from CFG

- Finds ambiguities in the grammar

- Lexer often written by hand

#### Parser Generators

- Writing parsers by hand can be large effort

- ▶ Parser generators can simplify parser writing a lot

- ► Yacc/Bison, PLY, ANTLR, ...

- Automatic generation of parser/parsing tables from CFG

- Finds ambiguities in the grammar

- Lexer often written by hand

- Used heavily in practice, unless error handling is important

#### Bison Example - part 1

```

%define api.pure full

%define api.value.type {ASTNode*}

%param { Lexer* lexer }

%code{

static int yylex(ASTNode ** lvalp, Lexer* lexer);

%token NUMBER

%token WHILE "while"

%token BREAK "break"

// precedence and associativity

%right '='

%left '+'

%left '*'

```

### Bison Example – part 2

```

%%

stmt : WHILE '(' expr ')' stmt { $$ = mkNode(WHILE, $1, $2); }

| BREAK ':'

{ $$ = mkNode(BREAK, NULL, NULL); }

\{ \$\$ = \$1; \}

expr ';'

\{ \$\$ = mkNode('+', \$1, \$2); \}

expr : expr '+' expr

\{ \$\$ = mkNode('*', \$1, \$2); \}

| expr '*' expr

\{ \$\$ = mkNode('=', \$1, \$2); \}

| '(' expr ')'

\{ \$\$ = \$1; \}

I NUMBER

%%

static int yvlex(ASTNode** lvalp, Lexer* lexer) {

/* return next token, or YYEOF/... */ }

```

➤ Some use parser generators, e.g. Python some use hand-written parsers, e.g. GCC, Clang, Swift, Go

- ➤ Some use parser generators, e.g. Python some use hand-written parsers, e.g. GCC, Clang, Swift, Go

- Optimization of grammar for performance

- ► Rewrite rules to reduce states, etc.

- ▶ Some use parser generators, e.g. Python some use hand-written parsers, e.g. GCC, Clang, Swift, Go

- Optimization of grammar for performance

- Rewrite rules to reduce states, etc.

- Useful error-handling: complex!

- Try skipping to next separator, e.g.; or,

- ▶ Some use parser generators, e.g. Python some use hand-written parsers, e.g. GCC, Clang, Swift, Go

- Optimization of grammar for performance

- Rewrite rules to reduce states, etc.

- Useful error-handling: complex!

- Try skipping to next separator, e.g.; or,

- Programming languages are not always context-free

- C: foo\* bar;

- May need to break separation between lexer and parser

► C++ is not context-free (inherited from C): T \* a;

- ► C++ is not context-free (inherited from C): T \* a;

- ► C++ is ambiguous: Type (a), b;

- ► Can be a declaration or a comma expression

- ► C++ is not context-free (inherited from C): T \* a;

- ► C++ is ambiguous: Type (a), b;

- Can be a declaration or a comma expression

- ► C++ templates are Turing-complete<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>TL Veldhuizen. C++ templates are Turing complete. 2003. ⊚.

- ► C++ is not context-free (inherited from C): T \* a;

- ► C++ is ambiguous: Type (a), b;

- Can be a declaration or a comma expression

- ► C++ templates are Turing-complete<sup>3</sup>

- ► C++ parsing is hence undecidable<sup>4</sup>

- ► Template instantiation combined with C T \* a ambiguity

<sup>3</sup>TL Veldhuizen. C++ templates are Turing complete. 2003. ⊚.

<sup>&</sup>lt;sup>4</sup>J Haberman. Parsing C++ is literally undecidable. 2013. ⊚.

## Semantic Analysis

### Semantic Analysis

- Needs context-sensitive analysis:

- ► Variable existence, storage, accessibility, . . .

- Function existence, arguments, . . .

- Operator type compatibility

- Attribute allowance

- Additional type complexity: inference, polymorphism, . . .

## Semantic Analysis: Scope Checking with AST Walking

- ▶ Idea: walk through AST (in DFS-order) and validate on the way

- Keep track of scope with declared variables

- Might need to keep track of defined types separately

## Semantic Analysis: Scope Checking with AST Walking

- ▶ Idea: walk through AST (in DFS-order) and validate on the way

- Keep track of scope with declared variables

- ▶ Might need to keep track of defined types separately

How to implement the scope data structure?

## Semantic Analysis: Scope Checking with AST Walking

- ▶ Idea: walk through AST (in DFS-order) and validate on the way

- ► Keep track of scope with declared variables

- Might need to keep track of defined types separately

#### How to implement the scope data structure?

- ► For identifiers: check existence and get type

- ► For expressions: check types and derive result type

- ► For assignment: check Ivalue-ness of left side

- Might be possible during AST creation

- ► Needs care with built-ins and other special constructs

## Semantic Analysis and Post-Parsing Transformations

- ► Check for error-prone code patterns

- ▶ Completeness of switch, out-of-range constants, unused variables, ...

- Check method calls, parameter types

- Duplicate code for templates

- ► Make implicit value conversions explicit

- Handle attributes: visibility, warnings, etc.

- ▶ Mangle names, split functions (OpenMP), ABI-specific setup, ...

- ► Last step: generate IR code

- ► Not necessarily: normal compilers

- ► Some languages (e.g., Rust) need unbounded time for parsing

- ► Not necessarily: normal compilers

- ► Some languages (e.g., Rust) need unbounded time for parsing

- Somewhat: JIT compilers

- ► Start-up time is generally noticable

- ► Not necessarily: normal compilers

- ► Some languages (e.g., Rust) need unbounded time for parsing

- ► Somewhat: JIT compilers

- ► Start-up time is generally noticable

- Somewhat more: Developer tools

- ▶ Imagine: waiting for seconds just for updated syntax highlighting

- Often uses tricks like incremental updates to parse tree

### Data Types

- ▶ Important part of programming languages

- Might have large variety and compatibility

- Numbers, Strings, Arrays, Compound Types (struct/union), Enum, Templates, Functions, Pointers, . . .

- ► Class hierarchy, Interfaces, Abstract Classes, . . .

- ▶ Integer/float compatibility, promotion, . . .

- Might have implicit conversions

- ► Simple class/struct: trivial, just bunch of fields

- ▶ Methods take (pointer to) this as implicit parameter

- ► Single inheritance: also trivial extend struct at end

- ► Simple class/struct: trivial, just bunch of fields

- Methods take (pointer to) this as implicit parameter

- ► Single inheritance: also trivial extend struct at end

- Virtual methods: store vtable in object representation

- vtable = table of function pointers for virtual methods

- ► Each sub-class has their own vtable

- ► Simple class/struct: trivial, just bunch of fields

- ▶ Methods take (pointer to) this as implicit parameter

- ► Single inheritance: also trivial extend struct at end

- Virtual methods: store vtable in object representation

- vtable = table of function pointers for virtual methods

- ► Each sub-class has their own vtable

- Multiple inheritance is much more involved

- Simple class/struct: trivial, just bunch of fields

- Methods take (pointer to) this as implicit parameter

- ► Single inheritance: also trivial extend struct at end

- Virtual methods: store vtable in object representation

- vtable = table of function pointers for virtual methods

- ► Each sub-class has their own vtable

- Multiple inheritance is much more involved

- Dynamic casts: needs run-time type information (RTTI)

#### Recommended Lectures

AD IN2227 "Compiler Constructions" covers parsing/analysis in depth

AD CIT3230000 "Programming Languages" covers dispatching/mixins/...

### Compiler Front-end – Summary

- Lexer splits input into tokens

- ► Essentially Regex-Matching + Keywords; rather simple

- Parser constructs (abstract) syntax tree from tokens

- Top-down vs. bottom-up parsing

- ► Typical: top-down for control flow; bottom-up for expressions

- Respect precedence and associativity for operators

- Semantic analysis ensures meaningful program

- Some data structures are complex to implement

- Some programming languages are more difficult to parse

### Compiler Front-end – Questions

- ▶ What are typical components of a compiler front-end?

- What output does the lexer produce?

- How does a parser disambiguate rules?

- What is the typical way to handle operator precedence?

- Why are not all programming languages describable using CFGs?

- How to implement classes with virtual functions?

## Code Generation for Data Processing

Lecture 3: Intermediate Representations

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2024/25

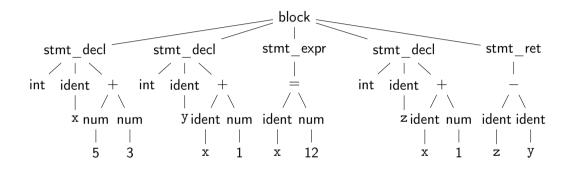

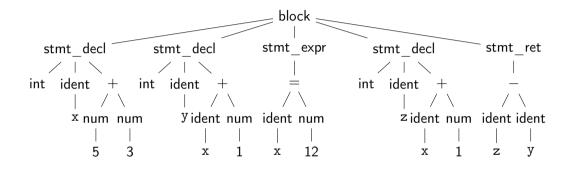

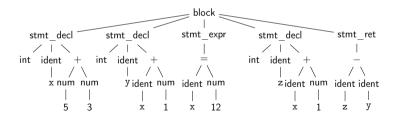

- ► So far: program parsed into AST

- + Great for language-related checks

- + Easy to correlate with original source code (e.g., errors)

- Hard for analyses/optimizations due to high complexity

- variable names, control flow constructs, etc.

- Data and control flow implicit

- Highly language-specific

Question: how to optimize? Is x+1 redundant?

Question: how to optimize? Is x+1 redundant? → hard to tell ∴

Question: how to optimize? Is x+1 redundant?

Question: how to optimize? Is x+1 redundant?  $\rightsquigarrow$  No! :

### Intermediate Representations

- Definitive program representation inside compiler

- During compilation, only the (current) IR is considered

- ► Goal: simplify analyses/transformations

- Technically, single-step compilation is possible for, e.g., C

but optimizations are hard without proper IRs

- Compilers design IRs to support frequent operations

- ► IR design can vary strongly between compilers

- Typically based on graphs or linear instructions (or both)

## Compiler Design: Effect of Languages – Imperative

- Step-by-step execution of program modification of state

- Close to hardware execution model

- Direct influence of result

- ► Tracking of state is complex

- Dynamic typing: more complexity

- Limits optimization possibilities

```

void addvec(int* a, const int* b) {

for (unsigned i = 0; i < 4; i++)

a[i] += b[i]; // vectorizable?

}

func:

mov [rdi], rsi

mov [rdi+8], rdx</pre>

```

mov [rdi], 0 // redundant?

ret

## Compiler Design: Effect of Languages – Declarative

- Describes execution target

- Compiler has to derive good mapping to imperative hardware

- Allows for more optimizations

- Mapping to hardware non-trivial

- Might need more stages

- Preserve semantic info for opt!

- ► Programmer has less "control"

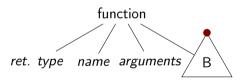

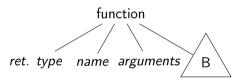

# Graph IRs: Abstract Syntax Tree (AST)

- Code representation close to the source

- Representation of types, constants, etc. might differ

- Storage might be problematic for large inputs

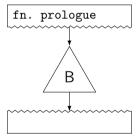

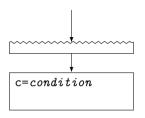

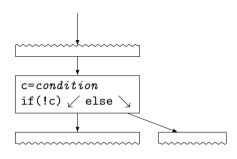

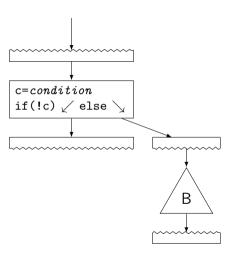

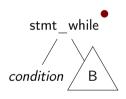

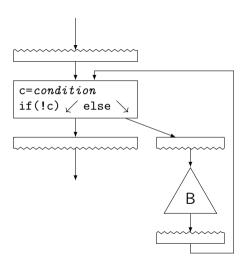

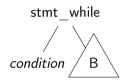

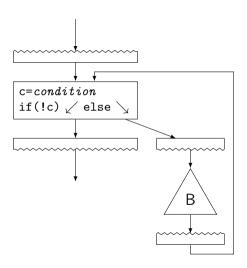

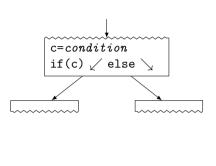

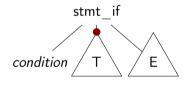

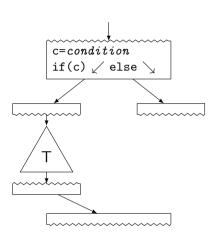

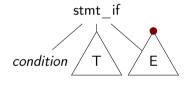

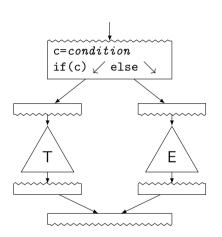

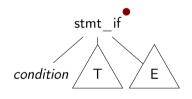

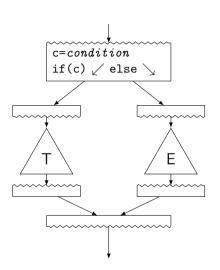

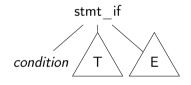

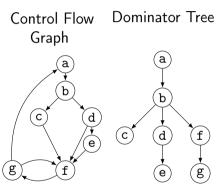

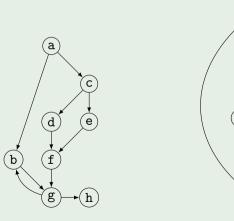

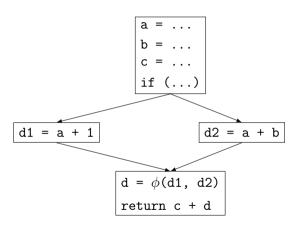

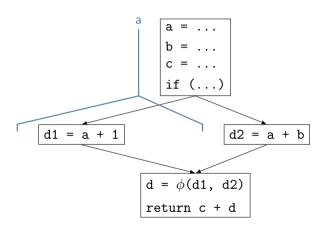

# Graph IRs: Control Flow Graph (CFG)

- Motivation: model control flow between different code sections

- ► Graph nodes represent basic blocks

- ▶ Basic block: sequence of branch-free code (modulo exceptions)

- Typically represented using a linear IR

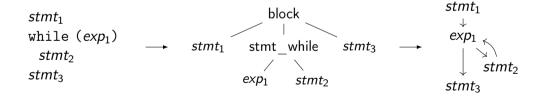

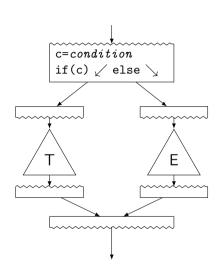

▶ Idea: Keep track of current insert block while walking through AST

fn. prologue

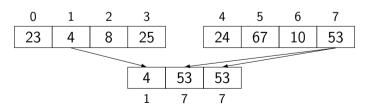

## Build CFG from AST: Switch

#### Build CFG from AST: Switch

#### Linear search

```

t \leftarrow \exp

if t == 3: goto B_3

if t == 4: goto B_4

if t == 7: goto B_7

if t == 9: goto B_9

goto B_D

```

#### Binary search

```

t \leftarrow \exp

if t == 7: goto B_7

elif t > 7:

if t == 9: goto B_9

else:

if t == 3: goto B_3

if t == 4: goto B_4

goto B_D

```

#### Jump table

```

\begin{array}{l} \texttt{t} \leftarrow \texttt{exp} \\ \texttt{if} \ 0 \leq \texttt{t} < \texttt{10:} \\ \texttt{goto table[t]} \\ \texttt{goto } B_D \\ \\ \texttt{table} = \{ \\ B_D, \ B_D, \ B_D, \ B_3, \\ B_4, \ B_D, \ \dots \ \} \end{array}

```

### Build CFG from AST: Switch

#### Linear search

```

t \leftarrow \exp

if t == 3: goto B_3

if t == 4: goto B_4

if t == 7: goto B_7

if t == 9: goto B_9

goto B_D

```

- + Trivial

- Slow, lot of code

#### Binary search

```

t \leftarrow \exp

if t == 7: goto B_7

elif t > 7:

if t == 9: goto B_9

else:

if t == 3: goto B_3

if t == 4: goto B_4

goto B_D

```

- + Good: sparse values

- Even more code

#### Jump table

```

t \leftarrow \exp

if 0 \le t < 10:

goto table[t]

goto B_D

table = {

B_D, B_D, B_D, B_3, B_4, B_0, \dots}

```

- + Fastest

- Table can be large, needs ind. jump

## Build CFG from AST: Break, Continue, Goto

- break/continue: trivial

- ► Keep track of target block, insert branch

- goto: also trivial

- Split block at target label, if needed

- ▶ But: may lead to irreducible control flow graph (see later)

#### CFG: Formal Definition

- ▶ Flow graph: G = (N, E, s) with a digraph (N, E) and entry  $s \in N$

- Each node is a basic block, s is the entry block

- $ightharpoonup (n_1, n_2) \in E$  iff  $n_2$  might be executed immediately after  $n_1$

- ▶ All  $n \in N$  shall be reachable from s (unreachable nodes can be discarded)

- Nodes without successors are end points

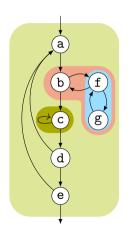

## CFG from C – Example

Derive the CFG for the these functions. Assume a switch instruction exists.

```

int fn1() {

if (a()) {

while (b()) {

c();

if (d())

continue;

e();

} else {

f();

```

```

int fn2() {

a();

do switch (c()) {

case 1:

while (d()) {

e();

case 2:

f();

default:

g();

} while (h());

return b();

```

# Graph IRs: Call Graph

Graph showing (possible) call relations between functions

## Graph IRs: Call Graph

- Graph showing (possible) call relations between functions

- Useful for interprocedural optimizations

- Function ordering

- Stack depth estimation

- ...

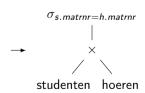

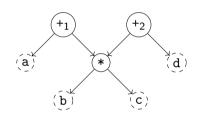

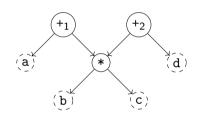

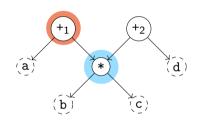

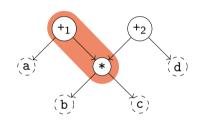

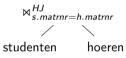

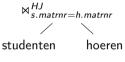

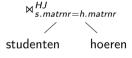

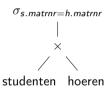

## Graph IRs: Relational Algebra

- ► Higher-level representation of query plans

- ► Explicit data flow

SELECT s.name, h.vorlnr FROM studenten s, hoeren h WHERE s.matrnr = h.matrnr

## Graph IRs: Relational Algebra

- Higher-level representation of query plans

- Explicit data flow

- ▶ Allow for optimization and selection actual implementations

- ► Elimination of common sub-trees

- Joins: ordering, implementation, etc.

SELECT s.name, h.vorlnr FROM studenten s, hoeren h WHERE s.matrnr = h.matrnr

## Graph IRs: Relational Algebra

- Higher-level representation of query plans

- Explicit data flow

- ▶ Allow for optimization and selection actual implementations

- ► Elimination of common sub-trees

- Joins: ordering, implementation, etc.

SELECT s.name, h.vorlnr FROM studenten s, hoeren h WHERE s.matrnr = h.matrnr

#### Linear IRs: Stack Machines

- Operands stored on a stack

- Operations pop arguments from top and push result

- Typically accompanied with variable storage

- Generating IR from AST: trivial

- ▶ Often used for bytecode, e.g. Java, Python

+

-

push 5 push 3 add pop x push x push 1 add pop y push 12 pop x push x push 1 add pop z

### Linear IRs: Stack Machines

- Operands stored on a stack

- Operations pop arguments from top and push result

- Typically accompanied with variable storage

- ► Generating IR from AST: trivial

- ▶ Often used for bytecode, e.g. Java, Python

- + Compact code, easy to generate and implement

- Performance, hard to analyze

push 5 push 3 add pop x push x push 1 add pop y push 12 pop x push x push 1 add pop z

# Linear IRs: Register Machines

- Operands stored in registers

- Operations read and write registers

- ► Typically: infinite number of registers

- ► Typically: three-address form

- ightharpoonup dst = src1 op src2

- ► Generating IR from AST: trivial

- ► E.g., GIMPLE, eBPF, Assembly

## Example: High GIMPLE

```

int fac (int n)

gimple_bind < // <-- still has lexical scopes</pre>

int D.1950:

int res;

int foo(int n) {

int res = 1:

gimple_assign <integer_cst, res, 1, NULL, NULL>

gimple_goto <<D.1947>>

while (n) {

gimple label << D.1948>>

res *= n * n:

gimple_assign <mult_expr, _1, n, n, NULL>

n = 1:

gimple_assign <mult_expr, res, res, _1, NULL>

gimple_assign <plus_expr, n, n, -1, NULL>

gimple_label <<D.1947>>

return res;

gimple_cond <ne_expr, n, 0, <D.1948>, <D.1946>>

gimple_label <<D.1946>>

gimple_assign <var_decl, D.1950, res, NULL, NULL>

gimple_return <D.1950>

$ gcc -fdump-tree-gimple-raw -c foo.c

```

## Example: Low GIMPLE

```

int fac (int n)

int res:

int D.1950;

int foo(int n) {

gimple_assign <integer_cst, res, 1, NULL, NULL>

int res = 1;

gimple_goto <<D.1947>>

gimple_label <<D.1948>>

while (n) {

gimple_assign <mult_expr, _1, n, n, NULL>

res *= n * n;

gimple_assign <mult_expr, res, res, _1, NULL>

n = 1:

gimple_assign <plus_expr, n, n, -1, NULL>

gimple_label <<D.1947>>

gimple_cond <ne_expr, n, 0, <D.1948>, <D.1946>>

return res:

gimple_label <<D.1946>>

gimple_assign <var_decl, D.1950, res, NULL, NULL>

gimple_goto <<D.1951>>

gimple_label <<D.1951>>

gimple_return <D.1950>

$ gcc -fdump-tree-lower-raw -c foo.c

```

### Example: Low GIMPLE with CFG

```

int fac (int n) {

int res:

int D.1950:

\langle hh 2 \rangle .

gimple_assign <integer_cst, res, 1, NULL, NULL>

goto <bb 4>; [INV]

int foo(int n) {

<bb 3> :

int res = 1:

gimple_assign <mult_expr, _1, n, n, NULL>

gimple_assign <mult_expr, res, res, _1, NULL>

while (n) {

gimple_assign <plus_expr, n, n, -1, NULL>

res *= n * n:

\langle bb | 4 \rangle:

n = 1:

gimple_cond <ne_expr, n, 0, NULL, NULL>

goto <bb 3>: [INV]

else

return res;

goto <bb 5>: [INV]

<bb >5> :

gimple_assign <var_decl, D.1950, res, NULL, NULL>

<bb 6> :

gimple_label <<L3>>

gimple_return <D.1950>

```

\$ gcc -fdump-tree-cfg-raw -c foo.c

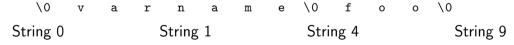

# Linear IRs: Register Machines

- ▶ Problem: no clear def—use information

- $\triangleright$  Is x+1 the same?

- ► Hard to track actual values!

- ► How to optimize?

# Linear IRs: Register Machines

- ▶ Problem: no clear def—use information

- $\triangleright$  Is x+1 the same?

- ► Hard to track actual values!

- ► How to optimize?

- ⇒ Disallow mutations of variables

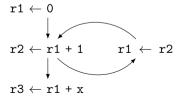

# Single Static Assignment: Introduction

- ▶ Idea: disallow mutations of variables, value set in declaration

- ▶ Instead: create new variable for updated value

- ► SSA form: every computed value has a unique definition

- ► Equivalent formulation: each name describes result of one operation

## Single Static Assignment: Introduction

- ▶ Idea: disallow mutations of variables, value set in declaration

- ► Instead: create new variable for updated value

- ► SSA form: every computed value has a unique definition

- ► Equivalent formulation: each name describes result of one operation

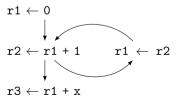

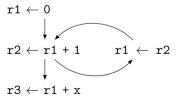

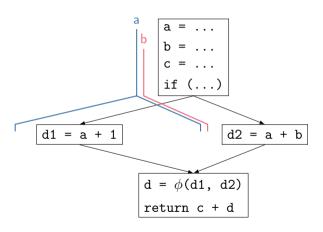

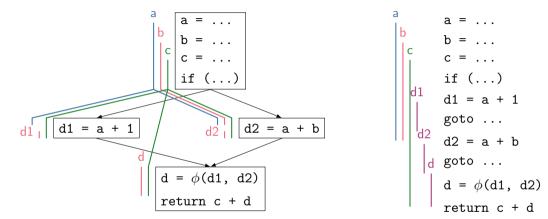

# Single Static Assignment: Control Flow

▶ How to handle diverging values in control flow?

```

entry: x \leftarrow \dots

if (x > 2) goto cont

then: x \leftarrow x * 2

cont: return x

```

# Single Static Assignment: Control Flow

▶ How to handle diverging values in control flow?

```

entry: x \leftarrow \dots

if (x > 2) goto cont \rightarrow

then: x \leftarrow x * 2

```

cont: return x

entry:  $v_1 \leftarrow \dots$ if  $(v_1 > 2)$  goto cont

then:  $v_2 \leftarrow v_1 * 2$ cont: return ???

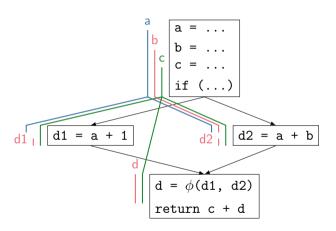

# Single Static Assignment: Control Flow

- How to handle diverging values in control flow?

- Solution: Φ-nodes to merge values depending on predecessor

- ► Value depends on edge used to enter the block

- ► All Φ-nodes of a block execute concurrently (ordering irrelevant)

```

entry: x \leftarrow \dots

if (x > 2) goto cont

then: x \leftarrow x * 2

cont: return x

entry: v_1 \leftarrow \dots

if (v_1 > 2) goto cont

then: v_2 \leftarrow v_1 * 2

cont: v_3 \leftarrow \Phi(\text{entry}: v_1, \text{then}: v_2)

return v_3

```

## Example: GIMPLE in SSA form

```

int fac (int n) { int res, D.1950, _1, _6;

\langle bb 2 \rangle:

gimple_assign <integer_cst, res_4, 1, NULL, NULL>

goto <bb 4>; [INV]

\langle bb 3 \rangle:

gimple_assign <mult_expr, _1, n_2, n_2, NULL>

int foo(int n) {

gimple_assign <mult_expr, res_8, res_3, _1, NULL>

int res = 1:

gimple_assign <plus_expr, n_9, n_2, -1, NULL>

<bb 4>:

while (n) {

# gimple_phi < n_2, n_5(D)(2), n_9(3) >

res *= n * n:

# gimple_phi <res_3, res_4(2), res_8(3)>

n = 1:

gimple_cond <ne_expr, n_2, 0, NULL, NULL>

goto <bb 3>: [INV]

else

return res;

goto <bb 5>: [INV]

<bb >5> :

gimple_assign <ssa_name, _6, res_3, NULL, NULL>

<bb 6> :

gimple_label <<L3>>

gimple_return <_6>

```

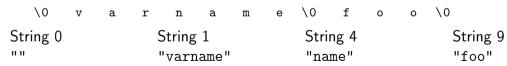

| Code |         |              |       |   |   | SSA | IR | Variable Mapping |

|------|---------|--------------|-------|---|---|-----|----|------------------|

|      | X       | $\leftarrow$ | 5     | + | 3 |     |    |                  |

|      | У       | $\leftarrow$ | X     | + | 1 |     |    |                  |

|      | X       | $\leftarrow$ | 12    |   |   |     |    |                  |

|      | Z       | $\leftarrow$ | X     | + | 1 |     |    |                  |

|      | $tmp_1$ | $\leftarrow$ | Z     | _ | У |     |    |                  |

|      | return  | tm           | $o_1$ |   |   |     |    |                  |

| Code          |         |              |    |       |   | 5 | SSA   | IR           |          | Variable Mapping |              |       |  |  |

|---------------|---------|--------------|----|-------|---|---|-------|--------------|----------|------------------|--------------|-------|--|--|

| $\rightarrow$ | X       | $\leftarrow$ | 5  | +     | 3 |   | $v_1$ | $\leftarrow$ | add 5, 3 | >                | $\leftarrow$ | $V_1$ |  |  |

|               | У       | $\leftarrow$ | X  | +     | 1 |   |       |              |          |                  |              | _     |  |  |

|               | X       | $\leftarrow$ | 12 |       |   |   |       |              |          |                  |              |       |  |  |

|               | Z       | $\leftarrow$ | X  | +     | 1 |   |       |              |          |                  |              |       |  |  |

|               | $tmp_1$ | $\leftarrow$ | Z  | _     | У |   |       |              |          |                  |              |       |  |  |

|               | return  |              | tm | $o_1$ |   |   |       |              |          |                  |              |       |  |  |

| Code          |                                      |                                                                                                   |                   | S     | Va | Variable Mapping |   |                                           |  |  |                                      |   |  |

|---------------|--------------------------------------|---------------------------------------------------------------------------------------------------|-------------------|-------|----|------------------|---|-------------------------------------------|--|--|--------------------------------------|---|--|

| $\rightarrow$ | x<br>y<br>x<br>z<br>tmp <sub>1</sub> | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$ | x<br>12<br>x<br>z | + + - | 1  |                  | _ | add 5, 3<br>add <i>v</i> <sub>1</sub> , 1 |  |  | $\overset{\rightarrow}{\rightarrow}$ | - |  |

|               | return                               |                                                                                                   | LITI              | $o_1$ |    |                  |   |                                           |  |  |                                      |   |  |

| Code                                                                                     |             |                   |       | S | Variable Mapping |       |              |                                 |  |  |                                      |   |   |

|------------------------------------------------------------------------------------------|-------------|-------------------|-------|---|------------------|-------|--------------|---------------------------------|--|--|--------------------------------------|---|---|

| $egin{array}{ccccc} x & \leftrightarrow & & & & \leftrightarrow & & & & & & & & & & & &$ | _<br>_<br>_ | x<br>12<br>x<br>z | + + - | 1 |                  | $v_2$ | $\leftarrow$ | add 5, 3 add $v_1$ , 1 const 12 |  |  | $\overset{\rightarrow}{\rightarrow}$ | • | ! |

| Code          |                          |                                                                                     |                   |       |   | SSA                                         | Varia                      | Variable Mapping                                       |   |                                                                                          |       |  |

|---------------|--------------------------|-------------------------------------------------------------------------------------|-------------------|-------|---|---------------------------------------------|----------------------------|--------------------------------------------------------|---|------------------------------------------------------------------------------------------|-------|--|

| $\rightarrow$ | x y x z tmp <sub>1</sub> | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$ | x<br>12<br>x<br>z | + + - | 1 | <i>V</i> <sub>2</sub> <i>V</i> <sub>3</sub> | $\leftarrow \\ \leftarrow$ | add 5, 3<br>add $v_1$ , 1<br>const 12<br>add $v_3$ , 1 | y | $ \begin{array}{ccc} x & \rightarrow \\ y & \rightarrow \\ z & \rightarrow \end{array} $ | $v_2$ |  |

| Code          |                                      |                                                                       |              | SSA | Variable Mapping |                                                                             |                                                        |                                                                             |   |                                                                                                        |                                             |  |

|---------------|--------------------------------------|-----------------------------------------------------------------------|--------------|-----|------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------|---------------------------------------------|--|

| $\rightarrow$ | x<br>y<br>x<br>z<br>tmp <sub>1</sub> | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$ | x<br>12<br>x | +   | 1                | <ul><li>V<sub>2</sub></li><li>V<sub>3</sub></li><li>V<sub>4</sub></li></ul> | $\leftarrow \\ \leftarrow \\ \leftarrow \\ \leftarrow$ | add 5, 3<br>add $v_1$ , 1<br>const 12<br>add $v_3$ , 1<br>sub $v_4$ , $v_2$ | y | $\begin{array}{c} \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \end{array}$ | <i>v</i> <sub>2</sub> <i>v</i> <sub>4</sub> |  |

|               | return                               |                                                                       | tm           | D1  |                  |                                                                             |                                                        |                                                                             |   |                                                                                                        |                                             |  |

| Code          |             |                            |                |   |   | SSA                              | IR                         | Variable Mapping                      |                      |                                                                                         |                                             |  |

|---------------|-------------|----------------------------|----------------|---|---|----------------------------------|----------------------------|---------------------------------------|----------------------|-----------------------------------------------------------------------------------------|---------------------------------------------|--|

|               | x<br>y<br>x | $\leftarrow \\ \leftarrow$ | <i>x</i><br>12 | + | 1 | v <sub>2</sub><br>v <sub>3</sub> | $\leftarrow \\ \leftarrow$ | add 5, 3<br>add $v_1$ , 1<br>const 12 | <i>y</i><br><i>z</i> | $\begin{array}{c} \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \end{array}$ | <i>V</i> <sub>2</sub> <i>V</i> <sub>4</sub> |  |

|               | $z$ $tmp_1$ |                            |                |   |   | •                                |                            | add $v_3$ , 1 sub $v_4$ , $v_2$       | $tmp_1$              | $\rightarrow$                                                                           | <i>V</i> 5                                  |  |

| $\rightarrow$ | return      | tm                         | <b>D</b> 1     |   |   |                                  | ret $v_5$                  |                                       |                      |                                                                                         |                                             |  |

| Code |                  |       |                         | Variable Mapping |   |                                                    |                                                        |                                                                             |   |                                                                                                        |                                  |  |

|------|------------------|-------|-------------------------|------------------|---|----------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------|----------------------------------|--|

|      | x<br>y<br>x<br>z | ← ← ← | x<br>12<br>x            | +                | 1 | v <sub>2</sub><br>v <sub>3</sub><br>v <sub>4</sub> | $\leftarrow \\ \leftarrow \\ \leftarrow \\ \leftarrow$ | add 5, 3<br>add $v_1$ , 1<br>const 12<br>add $v_3$ , 1<br>sub $v_4$ , $v_2$ | У | $\begin{array}{c} \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \end{array}$ | v <sub>2</sub><br>v <sub>4</sub> |  |

|      | , -              |       | $np_1 \leftarrow z - y$ |                  |   | · ·                                                |                                                        | ret. Vs                                                                     |   |                                                                                                        |                                  |  |

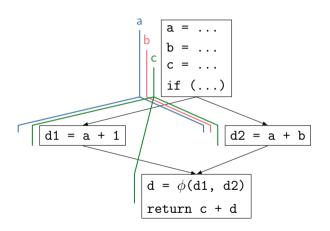

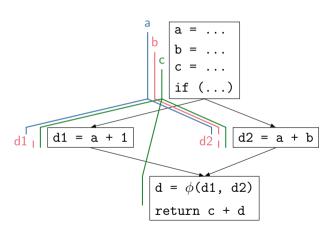

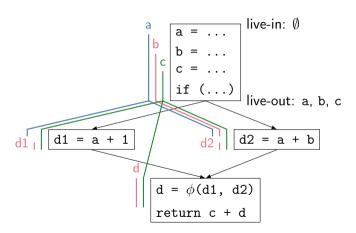

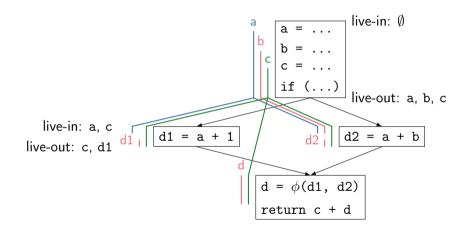

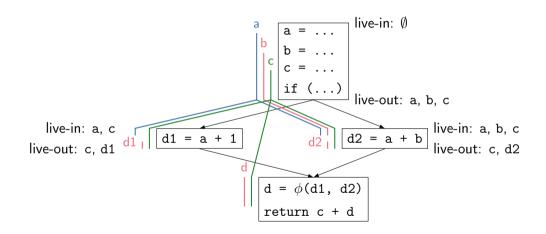

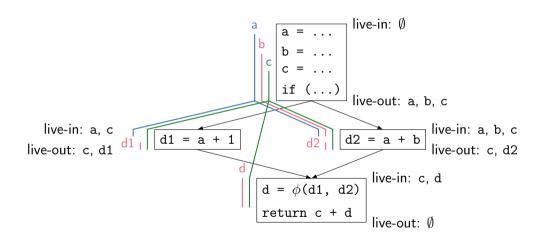

#### SSA Construction – Across Blocks

- SSA construction with control flow is non-trivial

- Key problem: find value for variable in predecessor

- Naive approach: Φ-nodes for all variables everywhere

- Create empty Φ-nodes for variables, populate variable mapping

- Fill blocks (as on last slide)

- Fill Φ-nodes with last value of variable in predecessor

#### SSA Construction – Across Blocks

- SSA construction with control flow is non-trivial

- Key problem: find value for variable in predecessor

- Naive approach: Φ-nodes for all variables everywhere

- Create empty Φ-nodes for variables, populate variable mapping

- Fill blocks (as on last slide)

- Fill Φ-nodes with last value of variable in predecessor

- Why is this a bad idea?

$\Rightarrow$  don't do this!

Extremely inefficient, code size explosion, many dead Φ

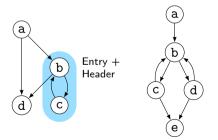

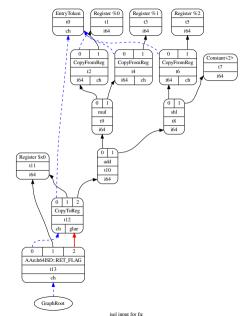

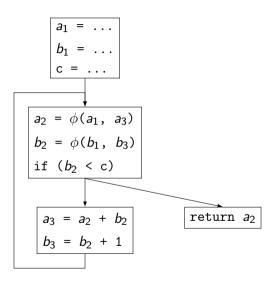

# SSA Construction – Across Blocks ("simple"<sup>5</sup>)

- Key problem: find value in predecessor

- ▶ Idea: seal block once all direct predecessors are known

- For acyclic constructs: trivial

- ► For loops: seal header once loop block is generated

- Current block not sealed: add Φ-node, fill on sealing

- Single predecessor: recursively query that

- Multiple preds.: add Φ-node, fill now

func  $foo(v_1)$

```

int foo(int n) {

int res = 1;

while (n) {

res *= n * n;

n -= 1;

}

return res;

}

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1

int foo(int n) {

int res = 1;

while (n) {

res *= n * n;

n = 1:

return res;

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

int foo(int n) {

int res = 1;

while (n) {

res *= n * n;

n = 1:

return res;

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header: NOT sealed; varmap: \emptyset

int foo(int n) {

int res = 1;

while (n) {

body:

NOT sealed; varmap: \emptyset

res *= n * n;

n = 1:

return res;

cont:

NOT sealed: varmap: 0

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed; varmap: \emptyset

int foo(int n) {

v_3 \leftarrow \text{equal } ???. 0

int res = 1;

while (n) {

body:

NOT sealed; varmap: \emptyset

res *= n * n;

n = 1:

return res;

cont:

NOT sealed: varmap: 0

```

```

func foo(v_1)

entry:

sealed: varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed; varmap: n \rightarrow \phi_1

int foo(int n) {

\phi_1 \leftarrow \phi incomplete, for n

v_3 \leftarrow \text{equal } \phi_1, 0

int res = 1;

while (n) {

res *= n * n;

bodv:

NOT sealed: varmap: \emptyset

n = 1:

return res;

```

cont:

NOT sealed; varmap:  $\emptyset$

```

func foo(v_1)

entry:

sealed: varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed; varmap: n \rightarrow \phi_1

int foo(int n) {

\phi_1 \leftarrow \phi incomplete, for n

v_3 \leftarrow \text{equal } \phi_1, 0

int res = 1;

while (n) {

br v3. cont. body

res *= n * n;

body:

NOT sealed: varmap: \emptyset

n = 1:

return res;

```

cont:

NOT sealed; varmap:  $\emptyset$

```

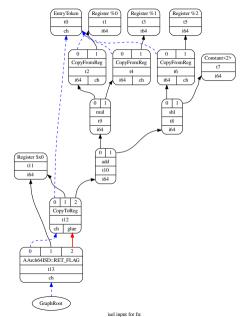

func foo(v_1)

entry:

sealed: varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed; varmap: n \rightarrow \phi_1

int foo(int n) {

\phi_1 \leftarrow \phi incomplete, for n

v_3 \leftarrow \text{equal } \phi_1, 0

int res = 1;

while (n) {

br v3. cont. body

res *= n * n;

body:

sealed; varmap: ∅

n = 1:

return res;

```

cont: NOT sealed; varmap:  $\emptyset$

```

func foo(v_1)

entry:

sealed: varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed; varmap: n \rightarrow \phi_1

int foo(int n) {

\phi_1 \leftarrow \phi incomplete, for n

v_3 \leftarrow \text{equal } \phi_1, 0

int res = 1:

while (n) {

br v_3, cont. body

res *= n * n;

body:

sealed: varmap: 0

n = 1:

v_4 \leftarrow \text{mul } ???. ???

return res;

```

cont:

NOT sealed; varmap:  $\emptyset$

```

func foo(v_1)

entry:

sealed: varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed; varmap: n \rightarrow \phi_1

int foo(int n) {

\phi_1 \leftarrow \phi incomplete, for n

v_3 \leftarrow \text{equal } \phi_1, 0

int res = 1:

while (n) {

br v_3, cont. body

res *= n * n;

body:

sealed: varmap: n \rightarrow \phi_1

n = 1:

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res;

```

cont:

NOT sealed; varmap:  $\emptyset$

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed; varmap: n \rightarrow \phi_1

int foo(int n) {

\phi_1 \leftarrow \phi incomplete, for n

v_3 \leftarrow \text{equal } \phi_1, 0

int res = 1:

while (n) {

br v_3, cont. body

res *= n * n;

body:

sealed: varmap: \mathbf{n} \rightarrow \phi_1

n = 1:

v_4 \leftarrow \text{mul } \phi_1, \phi_1

v_5 \leftarrow \text{mul } ???. v_4

return res;

cont:

NOT sealed: varmap: ∅

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed: varmap: n \rightarrow \phi_1, res\rightarrow \phi_2

\phi_1 \leftarrow \phi incomplete, for n

int foo(int n) {

\phi_2 \leftarrow \phi incomplete, for res

int res = 1:

v_3 \leftarrow \text{equal } \phi_1, 0

while (n) {

br v_3, cont, body

res *= n * n;

n = 1:

bodv:

sealed: varmap: n \rightarrow \phi_1, res\rightarrow v_5

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res:

v_5 \leftarrow \text{mul } \phi_2, v_4

```

cont: NOT sealed; varmap:  $\emptyset$

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed: varmap: n \rightarrow \phi_1, res\rightarrow \phi_2

\phi_1 \leftarrow \phi incomplete, for n

int foo(int n) {

\phi_2 \leftarrow \phi incomplete, for res

int res = 1:

v_3 \leftarrow \text{equal } \phi_1, 0

while (n) {

br v_3, cont, body

res *= n * n;

n = 1:

bodv:

sealed: varmap: n \rightarrow v_6, res\rightarrow v_5

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res:

v_5 \leftarrow \text{mul } \phi_2, v_4

v_6 \leftarrow \text{sub } \phi_1. 1

cont:

NOT sealed; varmap: ∅

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

NOT sealed: varmap: n \rightarrow \phi_1, res\rightarrow \phi_2

\phi_1 \leftarrow \phi incomplete, for n

int foo(int n) {

\phi_2 \leftarrow \phi incomplete, for res

int res = 1:

v_3 \leftarrow \text{equal } \phi_1, 0

while (n) {

br v_3, cont, body

res *= n * n;

n = 1:

bodv:

sealed: varmap: n \rightarrow v_6, res\rightarrow v_5

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res:

v_5 \leftarrow \text{mul } \phi_2, v_4

v_6 \leftarrow \text{sub } \phi_1. 1

br header

cont:

NOT sealed; varmap: ∅

```

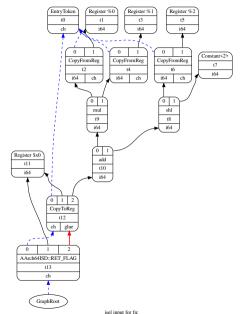

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

sealed; varmap: n \rightarrow \phi_1, res\rightarrow \phi_2

\phi_1 \leftarrow \phi incomplete, for n

int foo(int n) {

\phi_2 \leftarrow \phi incomplete, for res

int res = 1:

v_3 \leftarrow \text{equal } \phi_1, 0

while (n) {

br v_3, cont, body

res *= n * n;

n = 1:

bodv:

sealed: varmap: n \rightarrow v_6, res\rightarrow v_5

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res:

v_5 \leftarrow \text{mul } \phi_2, v_4

v_6 \leftarrow \text{sub } \phi_1. 1

br header

cont:

NOT sealed; varmap: ∅

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

sealed: varmap: n \rightarrow \phi_1, res\rightarrow \phi_2

\phi_1 \leftarrow \phi(\text{entry: } v_1, \text{body: } v_6)

int foo(int n) {

\phi_2 \leftarrow \phi(\text{entry: } v_2, \text{body: } v_5)

int res = 1:

v_3 \leftarrow \text{equal } \phi_1, 0

while (n) {

br v_3, cont, body

res *= n * n;

n = 1:

bodv:

sealed: varmap: n \rightarrow v_6, res\rightarrow v_5

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res:

v_5 \leftarrow \text{mul } \phi_2, v_4

v_6 \leftarrow \text{sub } \phi_1. 1

br header

cont:

NOT sealed; varmap: ∅

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

sealed: varmap: n \rightarrow \phi_1, res\rightarrow \phi_2

\phi_1 \leftarrow \phi(\text{entry: } v_1, \text{body: } v_6)

int foo(int n) {

\phi_2 \leftarrow \phi(\text{entry: } v_2, \text{body: } v_5)

int res = 1:

v_3 \leftarrow \text{equal } \phi_1, 0

while (n) {

br v_3, cont, body

res *= n * n;

n = 1:

bodv:

sealed: varmap: n \rightarrow v_6, res\rightarrow v_5

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res:

v_5 \leftarrow \text{mul } \phi_2, v_4

v_6 \leftarrow \text{sub } \phi_1. 1

br header

cont:

sealed: varmap: 0

```

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

sealed: varmap: n \rightarrow \phi_1, res\rightarrow \phi_2

\phi_1 \leftarrow \phi(\text{entry: } v_1, \text{body: } v_6)

int foo(int n) {

\phi_2 \leftarrow \phi(\text{entry: } v_2, \text{body: } v_5)

int res = 1:

v_3 \leftarrow \text{equal } \phi_1, 0

while (n) {

br v_3, cont, body

res *= n * n;

n = 1:

bodv:

sealed: varmap: n \rightarrow v_6, res\rightarrow v_5

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res:

v_5 \leftarrow \text{mul } \phi_2, v_4

v_6 \leftarrow \text{sub } \phi_1. 1

br header

cont:

sealed; varmap: res\rightarrow \phi_2

ret \phi_2

```

Construct an IR in SSA form for the following C code.

```

int phis(int a, in b){

a = a * b;

if (a > b * b) {

int c = 1:

while (a > 0)

a = a - c;

} else {

a = b * b:

return a;

```

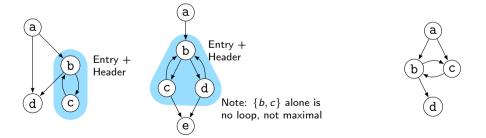

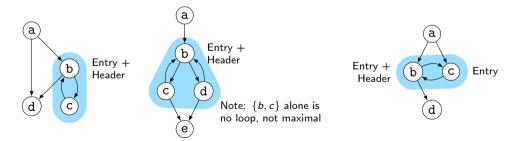

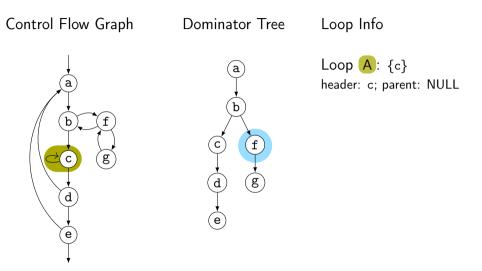

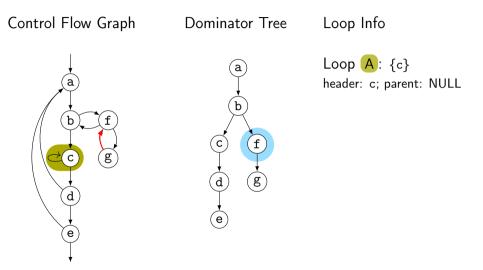

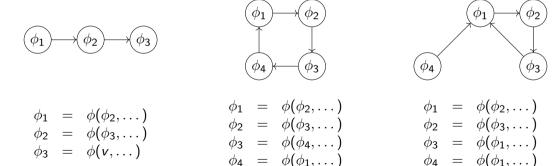

# SSA Construction – Pruned/Minimal Form

- ightharpoonup Resulting SSA is *pruned* all  $\phi$  are used

- ▶ But not minimal  $\phi$  nodes might have single, unique value

<sup>&</sup>lt;sup>6</sup>M Braun et al. "Simple and efficient construction of static single assignment form". In: CC. 2013, pp. 102–122. 🍥.

<sup>&</sup>lt;sup>7</sup>R Cytron et al. "Efficiently computing static single assignment form and the control dependence graph". In: *TOPLAS* 13.4 (1991), pp. 451–490.

# SSA Construction – Pruned/Minimal Form

- ightharpoonup Resulting SSA is *pruned* all  $\phi$  are used

- ightharpoonup But not minimal  $\phi$  nodes might have single, unique value

- lacktriangle When filling  $\phi$ , check that multiple real values exist

- lacktriangle Otherwise: replace  $\phi$  with the single value

- lacktriangle On replacement, update all  $\phi$  using this value, they might be trivial now, too

- ► Sufficient?

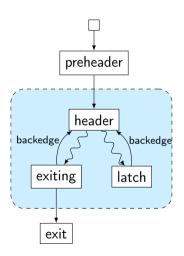

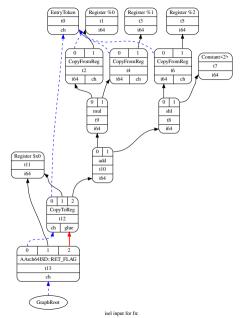

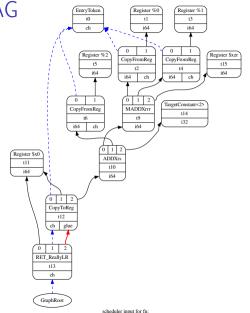

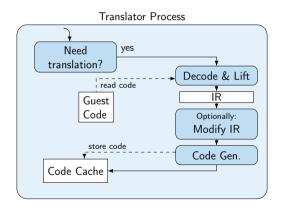

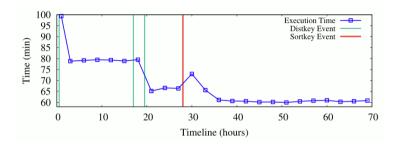

<sup>&</sup>lt;sup>6</sup>M Braun et al. "Simple and efficient construction of static single assignment form". In: CC. 2013, pp. 102–122. 🚱.