# **Programming Fully Disaggregated Systems**

Christoph Anneser, Lukas Vogel, Ferdinand Gruber, Maximilian Bandle, Jana Giceva School of Computation, Information and Technology Technical University of Munich

19<sup>th</sup> Workshop on Hot Topics in Operating Systems Providence, Rhode Island, USA 22–24 June 2023

DRAM

| Name         | Bw. | Lat. | Gran. | Attached | Sync  | Persist. |

|--------------|-----|------|-------|----------|-------|----------|

| Cache        | ++  | ++   | 1 B   | CPU      | 1     | X        |

| HBM          | ++  | +    | 64 B  | CPU      | 1     | X        |

| DRAM         | +   | +    | 64 B  | CPU      | 1     | X        |

| PMem         | 0   | 0    | 256 B | CPU      | 1     | 1        |

| CXL-DRAM     | 0   | 0    | 64 B  | PCle     | √ / X | √ / X    |

| Disagg. Mem. | 0   | _    | ?     | NIC      | X     | √ / X    |

| SSD          | _   | _    | 4 KiB | PCle     | X     | 1        |

| HDD          |     |      | 4 KiB | SATA     | ×     | 1        |

Table: Memory device properties as seen from a CPU.

| Table: Memory device properties as seen norma of 0. |     |      |       |          |       |          |

|-----------------------------------------------------|-----|------|-------|----------|-------|----------|

| Name                                                | Bw. | Lat. | Gran. | Attached | Sync  | Persist. |

| Cache                                               | ++  | ++   | 1 B   | CPU      | 1     | X        |

| HBM                                                 | ++  | +    | 64 B  | CPU      | 1     | X        |

| DRAM                                                | +   | +    | 64 B  | CPU      | 1     | X        |

| PMem                                                | 0   | 0    | 256 B | CPU      | 1     | 1        |

| CXL-DRAM                                            | 0   | 0    | 64 B  | PCle     | √ / X | √ / X    |

| Disagg. Mem.                                        | 0   | _    | ?     | NIC      | X     | √ / X    |

| SSD                                                 | _   | _    | 4 KiB | PCIe     | X     | 1        |

| HDD                                                 |     |      | 4 KiB | SATA     | ×     | 1        |

#### Table: Memory device properties as seen from a CPU.

#### $\Rightarrow$ How can we develop & optimize applications for heterogeneous, disaggregated environments?

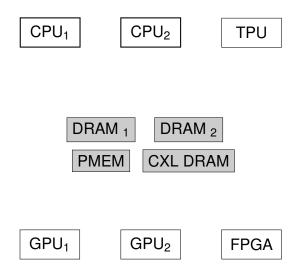

| CPU               | l <sub>1</sub> | CPU <sub>2</sub> |                 | TPU  |  |  |  |

|-------------------|----------------|------------------|-----------------|------|--|--|--|

| Abstraction Layer |                |                  |                 |      |  |  |  |

| Memory Pool       |                |                  |                 |      |  |  |  |

|                   | DRAM           | 1 DR             | AM <sub>2</sub> |      |  |  |  |

| PMEM CXL DRAM     |                |                  |                 |      |  |  |  |

|                   |                |                  |                 |      |  |  |  |

|                   |                |                  |                 |      |  |  |  |

| GPU               | l <sub>1</sub> | GPU <sub>2</sub> |                 | FPGA |  |  |  |

[1] Gay and Aiken: "Memory Management with Explicit Regions" (1998)

[3] Tofte and Talpin: "Region-based Memory Management" (1997)

[1] Gay and Aiken: "Memory Management with Explicit Regions" (1998)

[3] Tofte and Talpin: "Region-based Memory Management" (1997)

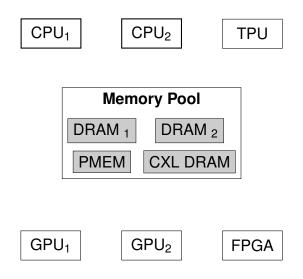

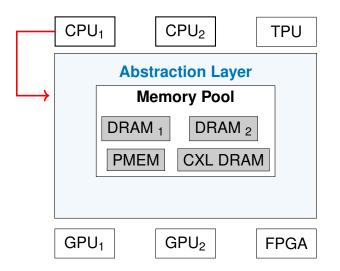

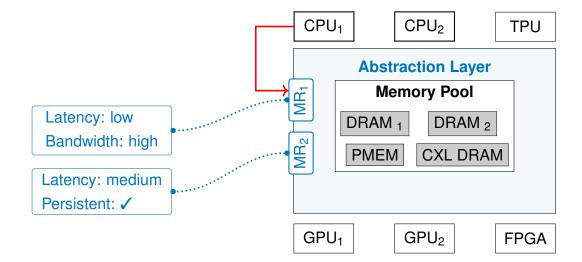

- Leverage memory regions [1, 3] as abstraction layer for disaggregated memory!

[1] Gay and Aiken: "Memory Management with Explicit Regions" (1998)

[3] Tofte and Talpin: "Region-based Memory Management" (1997)

- Leverage memory regions [1, 3] as abstraction layer for disaggregated memory!

[1] Gay and Aiken: "Memory Management with Explicit Regions" (1998)

[3] Tofte and Talpin: "Region-based Memory Management" (1997)

- Leverage memory regions [1, 3] as abstraction layer for disaggregated memory!

[1] Gay and Aiken: "Memory Management with Explicit Regions" (1998)

[3] Tofte and Talpin: "Region-based Memory Management" (1997)

- Leverage memory regions [1, 3] as abstraction layer for disaggregated memory!

[1] Gay and Aiken: "Memory Management with Explicit Regions" (1998)

[3] Tofte and Talpin: "Region-based Memory Management" (1997)

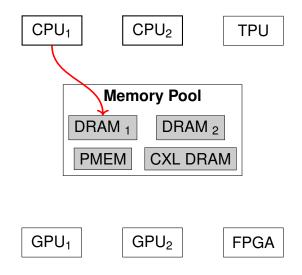

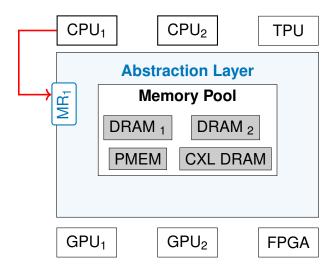

- Leverage **memory regions** [1, 3] as abstraction layer for disaggregated memory!

- Memory Regions are logical view on physical memory!

[1] Gay and Aiken: "Memory Management with Explicit Regions" (1998)

[3] Tofte and Talpin: "Region-based Memory Management" (1997)

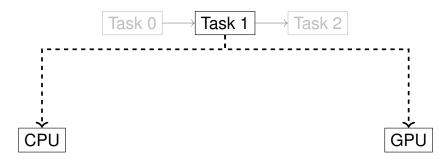

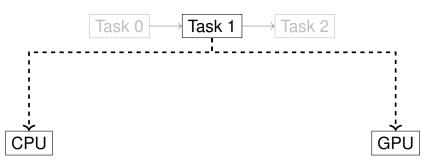

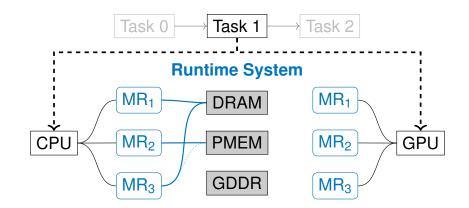

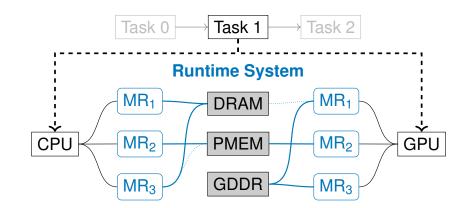

- Task Placement

- Task Placement

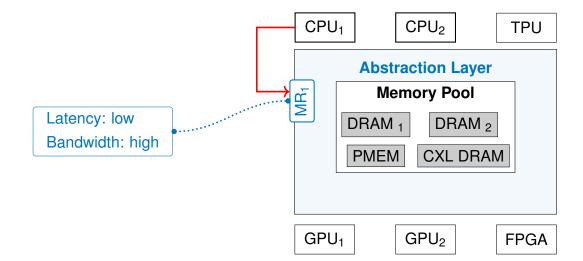

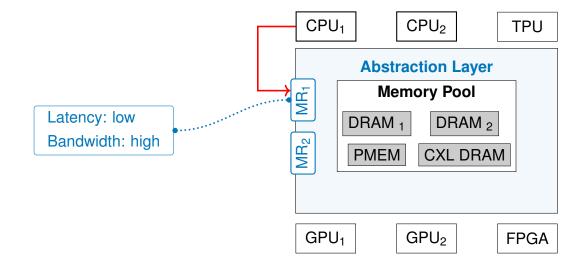

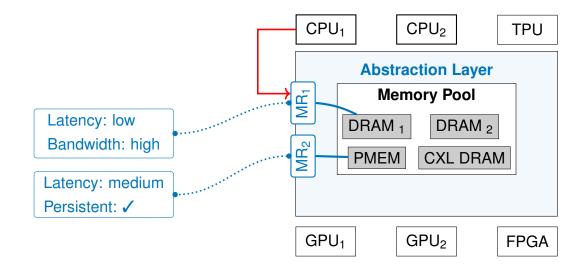

- Memory Region Properties:

MR<sub>1</sub>: low lat., sync

MR<sub>2</sub>: low lat., persistent, async

- Task Placement

- Memory Region Properties:

MR<sub>1</sub>: low lat., sync

MR<sub>2</sub>: low lat., persistent, async

- Task Placement

- Memory Region Properties:

MR<sub>1</sub>: low lat., sync MR<sub>2</sub>: low lat., persistent, async

- Task Placement

- Memory Region Properties:

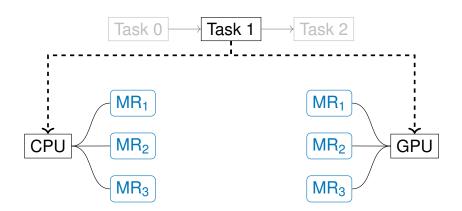

MR<sub>1</sub>: low lat., syncMR<sub>2</sub>: low lat., persistent, asyncMR<sub>3</sub>: low lat., high bandwith, sync

- Task Placement

- Memory Region Properties:

MR<sub>1</sub>: low lat., syncMR<sub>2</sub>: low lat., persistent, asyncMR<sub>3</sub>: low lat., high bandwith, sync

- Task Placement

- Memory Region Properties:

MR<sub>1</sub>: low lat., sync MR<sub>2</sub>: low lat., persistent, async

- Task Placement

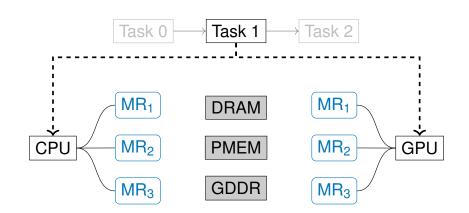

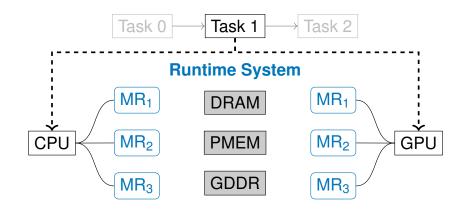

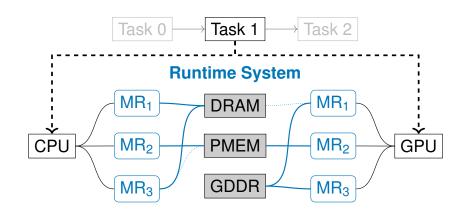

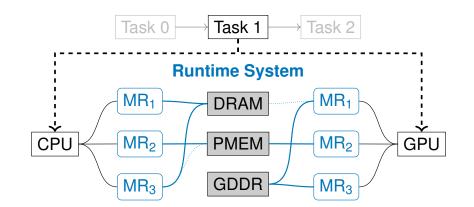

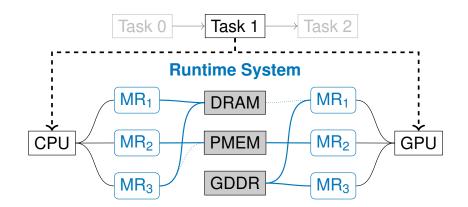

#### - Memory Region Properties:

MR<sub>1</sub>: low lat., syncMR<sub>2</sub>: low lat., persistent, asyncMR<sub>3</sub>: low lat., high bandwith, sync

#### - Handovers:

MR<sub>1</sub>: T0 Output, T1 Input MR<sub>2</sub>: T1 Output, T2 Input

- Task Placement

#### - Memory Region Properties:

MR<sub>1</sub>: low lat., syncMR<sub>2</sub>: low lat., persistent, asyncMR<sub>3</sub>: low lat., high bandwith, sync

#### - Handovers:

MR<sub>1</sub>: T0 Output, T1 Input MR<sub>2</sub>: T1 Output, T2 Input

#### Device Utilization

- Task Placement

#### - Memory Region Properties:

MR<sub>1</sub>: low lat., syncMR<sub>2</sub>: low lat., persistent, asyncMR<sub>3</sub>: low lat., high bandwith, sync

#### - Handovers:

MR<sub>1</sub>: T0 Output, T1 Input MR<sub>2</sub>: T1 Output, T2 Input

- Device Utilization

## Flexible mapping at runtime $\rightarrow$ Late Binding

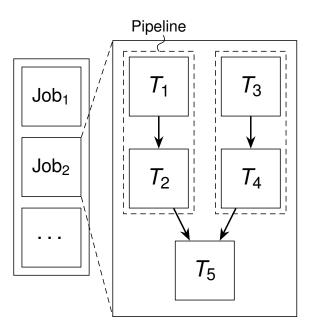

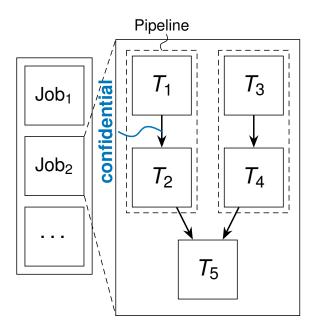

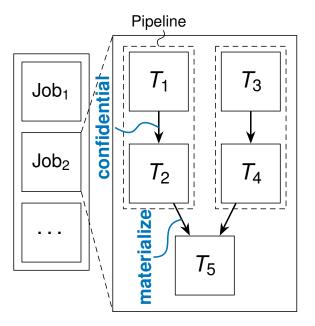

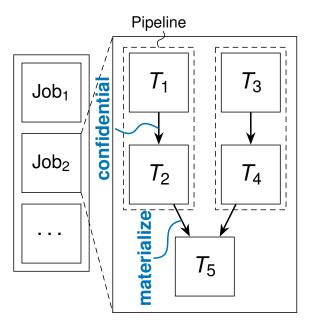

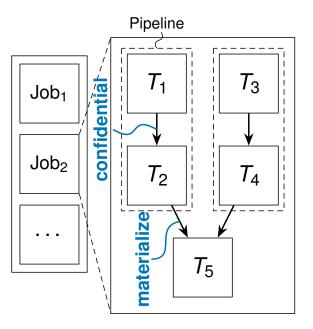

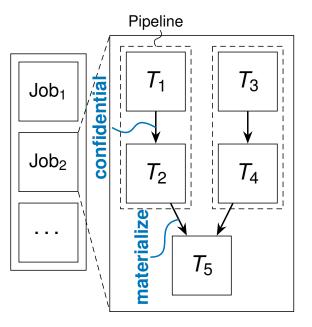

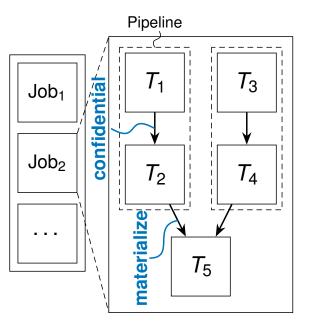

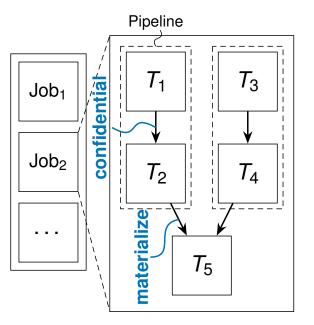

# **Dataflow Systems on Disaggregated Systems**

Declaratively attach properties to

# **Dataflow Systems on Disaggregated Systems**

#### Declaratively attach properties to

- Memory Regions

# **Dataflow Systems on Disaggregated Systems**

#### Declaratively attach properties to

- Memory Regions

- Tasks

# **Dataflow Systems on Disaggregated Systems**

#### Declaratively attach properties to

- Memory Regions

- Tasks

- Pipelines

# ПП

# **Dataflow Systems on Disaggregated Systems**

#### Declaratively attach properties to

- Memory Regions

- Tasks

- Pipelines

- Jobs

# ПП

# **Dataflow Systems on Disaggregated Systems**

#### Declaratively attach properties to

- Memory Regions

- Tasks

- Pipelines

- Jobs

- Applications

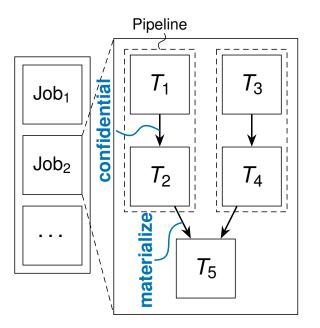

Dataflow applications use memory for ...

[2] Gog et al.: "Broom: Sweeping Out Garbage Collection from Big Data Systems" (2015)

Dataflow applications use memory for ...

#### ... Communication

- Purpose: Syncing tasks, message passing, ...

- Properties: coherent, sync

[2] Gog et al.: "Broom: Sweeping Out Garbage Collection from Big Data Systems" (2015)

Dataflow applications use memory for ...

... Communication

- Purpose: Syncing tasks, message passing, ...

- Properties: coherent, sync

$\Rightarrow$  Global State

[2] Gog et al.: "Broom: Sweeping Out Garbage Collection from Big Data Systems" (2015)

Dataflow applications use memory for ...

- ... Communication

- Purpose: Syncing tasks, message passing, ...

- Properties: coherent, sync

- ... Exchanging Data (e.g. Caching)

- Properties: coherent, async

$\Rightarrow$  Global State

[2] Gog et al.: "Broom: Sweeping Out Garbage Collection from Big Data Systems" (2015)

Dataflow applications use memory for ...

- ... Communication

- Purpose: Syncing tasks, message passing, ...

- Properties: coherent, sync

- ... Exchanging Data (e.g. Caching)

- Properties: coherent, async

$\Rightarrow$  Global State

$\Rightarrow$  Global Scratch

[2] Gog et al.: "Broom: Sweeping Out Garbage Collection from Big Data Systems" (2015)

Dataflow applications use memory for ...

- ... Communication

- Purpose: Syncing tasks, message passing, ...

- Properties: coherent, sync

- ... Exchanging Data (e.g. Caching)

- Properties: coherent, async

- ... Thread-local State

- Properties: non-coherent, sync, fast

$\Rightarrow$  Global State

$\Rightarrow$  Global Scratch

[2] Gog et al.: "Broom: Sweeping Out Garbage Collection from Big Data Systems" (2015)

Dataflow applications use memory for ...

- ... Communication

- Purpose: Syncing tasks, message passing, ...

- Properties: coherent, sync

- ... Exchanging Data (e.g. Caching)

- Properties: coherent, async

- ... Thread-local State

- Properties: non-coherent, sync, fast

$\Rightarrow$  Global State

$\Rightarrow$  Global Scratch

$\Rightarrow$  Private Scratch

[2] Gog et al.: "Broom: Sweeping Out Garbage Collection from Big Data Systems" (2015)

ПΠ

## Typed Memory Regions – cont'd

|  |  | Priv. Scratch | Glob. State | Glob. Scratch |

|--|--|---------------|-------------|---------------|

|--|--|---------------|-------------|---------------|

## **Typed Memory Regions – cont'd**

|      | Priv. Scratch                 | Glob. State              | Glob. Scratch             |

|------|-------------------------------|--------------------------|---------------------------|

| DBMS | operator state (hashtables, ) | synchronization (locks,) | (temp) indexes,<br>caches |

## **Typed Memory Regions – cont'd**

|       | Priv. Scratch  | Glob. State     | Glob. Scratch       |

|-------|----------------|-----------------|---------------------|

| DBMS  | operator state | synchronization | (temp) indexes,     |

|       | (hashtables,)  | (locks, )       | caches              |

| ML/AI | model training | metadata,       | input data,         |

|       | state          | worker state    | cached transf. data |

## **Typed Memory Regions – cont'd**

|       | Priv. Scratch  | Glob. State     | Glob. Scratch       |

|-------|----------------|-----------------|---------------------|

| DBMS  | operator state | synchronization | (temp) indexes,     |

|       | (hashtables,)  | (locks, )       | caches              |

| ML/AI | model training | metadata,       | input data,         |

|       | state          | worker state    | cached transf. data |

| HPC   | node-local     | job metadata,   | object/blob         |

|       | working mem.   | node states     | storage             |

## **Typed Memory Regions – cont'd**

|           | Priv. Scratch  | Glob. State     | Glob. Scratch       |

|-----------|----------------|-----------------|---------------------|

| DBMS      | operator state | synchronization | (temp) indexes,     |

|           | (hashtables,)  | (locks, )       | caches              |

| ML/AI     | model training | metadata,       | input data,         |

|           | state          | worker state    | cached transf. data |

| НРС       | node-local     | job metadata,   | object/blob         |

|           | working mem.   | node states     | storage             |

| Streaming | cache/buffer   | cluster/worker  | result/data         |

|           | (send, recv.)  | state           | cache               |

#### Lifetime Management of Memory Regions

## Lifetime Management of Memory Regions

ТШ

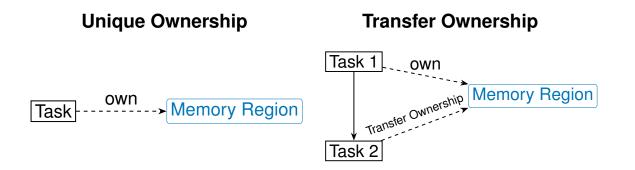

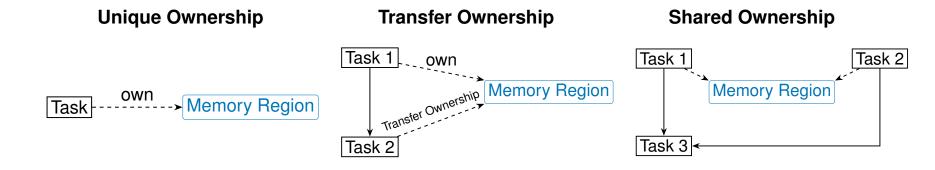

- Challenge: Memory Regions might outlive CPU/GPU/... Tasks/Processes

ПΠ

## Lifetime Management of Memory Regions

- Challenge: Memory Regions might outlive CPU/GPU/... Tasks/Processes

- **Ownership** of Memory Regions:

#### **Unique Ownership**

#### Lifetime Management of Memory Regions

- Challenge: Memory Regions might outlive CPU/GPU/... Tasks/Processes

- **Ownership** of Memory Regions:

## Lifetime Management of Memory Regions

- Challenge: Memory Regions might outlive CPU/GPU/... Tasks/Processes

- **Ownership** of Memory Regions:

٦Π

### **Our Vision**

#### We propose a new programming model:

(1) A memory-centric view based on logical memory regions

ΠП

## **Our Vision**

Challenge: Developing dataflow applications for fully disaggregated systems

#### We propose a new programming model:

- (1) A memory-centric view based on *logical memory regions*

- (2) Requesting memory declaratively based on properties

пп

## **Our Vision**

Challenge: Developing dataflow applications for fully disaggregated systems

#### We propose a new programming model:

- (1) A memory-centric view based on *logical memory regions*

- (2) Requesting memory *declaratively* based on properties

- (3) Typed memory regions

## **Our Vision**

Challenge: Developing dataflow applications for fully disaggregated systems

#### We propose a new programming model:

- (1) A memory-centric view based on logical memory regions

- (2) Requesting memory *declaratively* based on properties

- (3) Typed memory regions

- (4) A runtime system that co-optimizes data- and compute-placement

٦Π

### **The Way Forward**

#### How can we turn our vision into a programing model?

- (1) The Runtime System ...

- What functionality is required from the RTS?

πп

#### **The Way Forward**

#### How can we turn our vision into a programing model?

- (1) The Runtime System ...

- What functionality is required from the RTS?

- Where should the RTS/control plane be placed?

пп

### **The Way Forward**

#### How can we turn our vision into a programing model?

(1) The Runtime System ...

- What functionality is required from the RTS?

- Where should the RTS/control plane be placed?

- Page- or object-based memory allocations?

#### How can we turn our vision into a programing model?

(1) The Runtime System ...

- What functionality is required from the RTS?

- Where should the RTS/control plane be placed?

- Page- or object-based memory allocations?

- What layer supports the RTS memory deployment?

#### How can we turn our vision into a programing model?

(1) The Runtime System ...

- What functionality is required from the RTS?

- Where should the RTS/control plane be placed?

- Page- or object-based memory allocations?

- What layer supports the RTS memory deployment?

(2) The Programming Model ...

#### How can we turn our vision into a programing model?

(1) The Runtime System ...

- What functionality is required from the RTS?

- Where should the RTS/control plane be placed?

- Page- or object-based memory allocations?

- What layer supports the RTS memory deployment?

(2) The Programming Model ...

- Can we combine declarative and iterative concepts?

How can we turn our vision into a programing model?

(1) The Runtime System ...

- What functionality is required from the RTS?

- Where should the RTS/control plane be placed?

- Page- or object-based memory allocations?

- What layer supports the RTS memory deployment?

(2) The Programming Model ...

- Can we combine declarative and iterative concepts?

# Thank you for your attention!

anneser@in.tum.de

#### Sources

- [1] David Gay and Alexander Aiken. "Memory Management with Explicit Regions". In: *PLDI*. ACM, 1998, pp. 313–323.

- [2] Ionel Gog et al. "Broom: Sweeping Out Garbage Collection from Big Data Systems". In: HotOS. USENIX Association, 2015.

- [3] Mads Tofte and Jean-Pierre Talpin. "Region-based Memory Management". In: Inf. Comput. 132.2 (1997), pp. 109–176.

# ПП

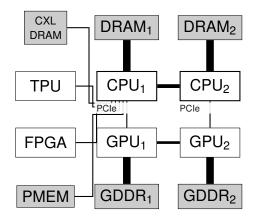

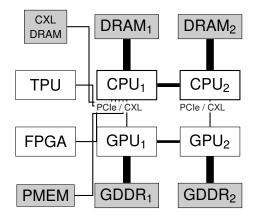

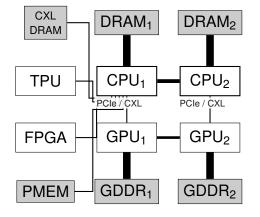

## Roadmap

- Set-up the testbed

- Machine with CXL-support (e.g. Intel's Sapphire Rapids)

- Identify suitable Workloads for CXL

- Dataflow over heterogeneous hardware

- Memory extension for large intermediate state

- Understand CXL's performance implications through benchmarks

- Design and implement the RTS key components & building blocks

- CXL-enabled vmcache, overcoming the accelerator's limited capacities

- Optimizer for data- and compute-placement